Intel

®

IXP42X product line and IXC1100 control plane processors—JTAG Interface

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

554 Order Number: 252480-006US

20.3 Data Registers

The Data Registers are essentially a shift register and a read/write register juxtaposed.

In other words, the shift register is used to shift data in and out and the read/write

register gets parallel loaded by the shift register during the Update-DR state and writes

back to the shift register (again, parallel-wise) during the Capture-DR state.

Typically, the data contained in the read/write registers are configuration bits, status

bits, or ID bits. The manner in which each data register is read and written, follows the

IEEE 1149.1 protocol using JTG_TDI, JTG_TDO, JTG_TMS, JTG_TRST_N, and JTG_TCK

signals. All the data registers (with the exception of the Instruction Register) can be

serially loaded with the corresponding data-register_write or data-register_read

instruction loaded in the JTAG Instruction Register along with the TAP Controller being

in the Shift-DR state.

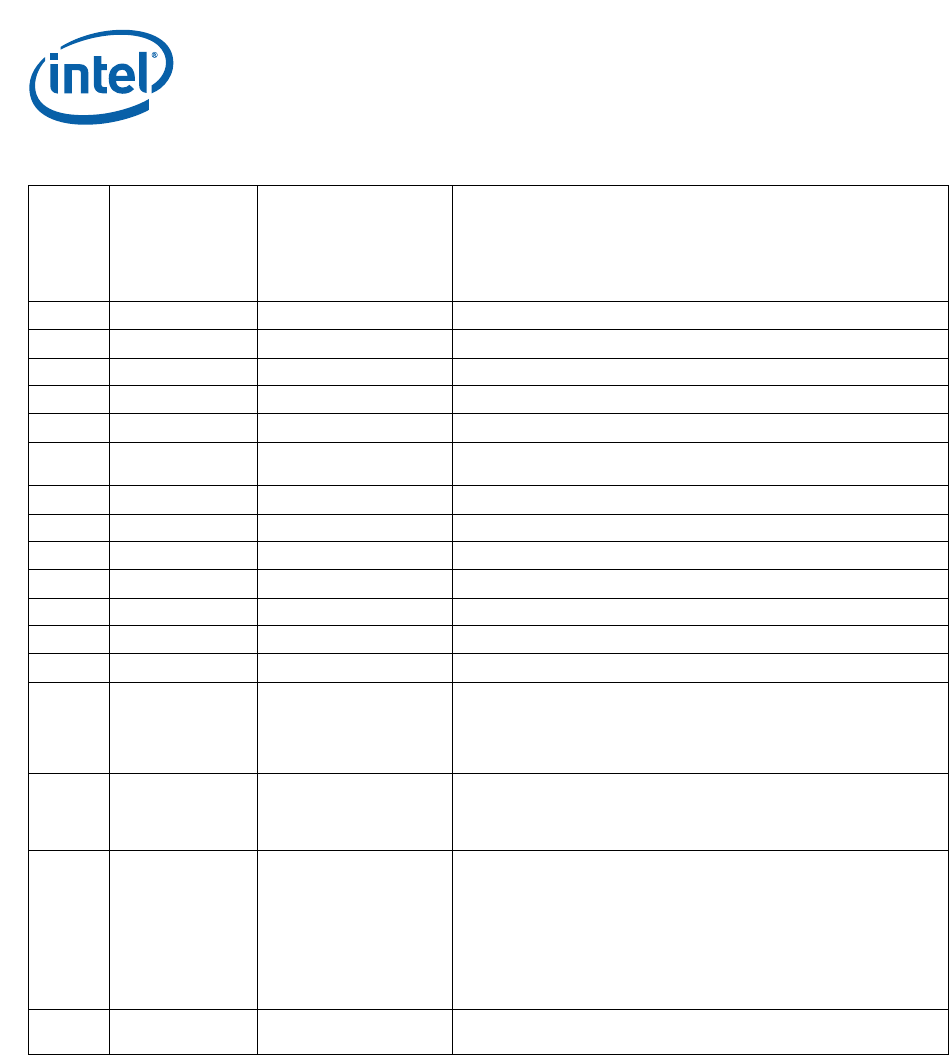

0000011 R Reserved Reserved

0000111 X LDIC Used for loading the Intel XScale processor instruction cache.

0001001 X DCSR Used for accessing the Debug Control/Status Register.

0001010 X BIST Used for Intel XScale processor BIST operation.

0001100 X SNAPDAT Used for putting Intel XScale processor into snapshot mode.

0010000 X DBGTX

Used for accessing the TX Debug Register within the Intel XScale

processor.

1000000 R Reserved Reserved

1000001 R Reserved Reserved

1000010 R Reserved Reserved

1000011 R Reserved Reserved

1000100 R Reserved Reserved

1000101 R Reserved Reserved

1000110 R Reserved Reserved

1001001 I BS_CLAMP

This instruction allows “guarding” values to be placed on the output

pins of a device while connecting the Bypass Register between TDI

and TDO in the shift_dr state. While the BS_CLAMP instruction is

selected, the state of all signals driven from system output pins is

defined by the data held in the Boundary Scan Register.

1001010 I HIGH_Z

The Highz instruction places the device in a state such that all

output and bidirectional pins are placed in an inactive drive state.

The Highz instruction connects the Bypass Register between TDI

and TDO in the shift_dr state.

1111110 X IDCODE

Connects the ID register in Intel XScale processor between TDI and

TDO during the TAP controller’s shift_dr state.

The IDCODE Register will be a 32-bit register and will contain the

following values when read:

533 MHz speed grade = 0x09274013

400 MHz speed grade = 0x09275013

266 MHz speed grade = 0x09277013

Any

Others

X BYPASS

All other instructions will connect a single bit Bypass Register

between TDI and TDO.

Table 174. JTAG Instruction Set (Sheet 2 of 2)

Op Code

Intel XScale

®

Processor or

IXP425 Op Code

(X= XScale,

I = IXP425,

R = Reserved)

Instruction Name Description