Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

224 Order Number: 252480-006US

1. An AHB master that wants to write a particular PCI Configuration Register writes

PCI_CRP_AD_CBE register first. Assume that the AHB master wants to write a

hexadecimal value of 0x85008086 to the Retry Timeout/TRDY Timeout

(PCI_RTOTTO) Register. The PCI_CRP_AD_CBE register is written with a

hexadecimal 0x00010040.

Note that bits 23:20 are set to hexadecimal 0. For write accesses byte enables are

active low. Bits 19:16 are set to hexadecimal 1, which denotes a write command.

Bits 7:0 are set to hexadecimal 40, which addresses the PCI_RTOTTO register.

2. Next, the hexadecimal value of 0x85008086 is written to the PCI Configuration

Register PCI_CRP_WDATA register, which causes the contents of the Retry

Timeout/TRDY Timeout (PCI_RTOTTO) Register to be written with a hexadecimal

value of 0x85008086.

One more example will demonstrate the effects of the byte-enables on write accesses

to the PCI Configuration Space:

1. Assume that the objective is to update the retry section of the Retry Timeout/TRDY

Timeout (PCI_RTOTTO) Register (Bits 15:8) without updating the TRDY terminal

count value of the Retry Timeout/TRDY Timeout (PCI_RTOTTO) Register (Bits 7:0).

The Retry Timeout/TRDY Timeout (PCI_RTOTTO) Register is located at hexadecimal

address 0x40. Also assume the value currently contained in the Retry Timeout/

TRDY Timeout (PCI_RTOTTO) Register is a hexadecimal 0x00008080.

2. The PCI_CRP_AD_CBE is written with hexadecimal 0x00D10040.

Note that bits 23:20 are set to hexadecimal D. For write accesses this allows only

byte 1 to be written (bits 15:8). Bits 19:16 are set to hexadecimal 1, which denotes

a write command. Bits 7:0 are set to hexadecimal 40, which addresses the

PCI_RTOTTO register.

3. Assume that the AHB master wants to write a hexadecimal value of 0x0000AB00 to

the second byte of the retry section of the Retry Timeout/TRDY Timeout

(PCI_RTOTTO) Register (Bits 15:8). The PCI_CRP_WDATA will be loaded with a

value of 0x0000AB00, which causes the contents of the retry section of the Retry

Timeout/TRDY Timeout (PCI_RTOTTO) Register (Bits 15:8) to be written with a

hexadecimal value of 0x0000AB00. The value that is now contained within the

Retry Timeout/TRDY Timeout (PCI_RTOTTO) Register is 0x0000AB80. Notice that

only one byte of data was manipulated.

Table 100 shows the PCI Byte Enables Byte Lane Mapping (accesses to the PCI

Configuration Space from within the IXP42X product line and IXC1100 control plane

processors) when using the CRP access mechanism.

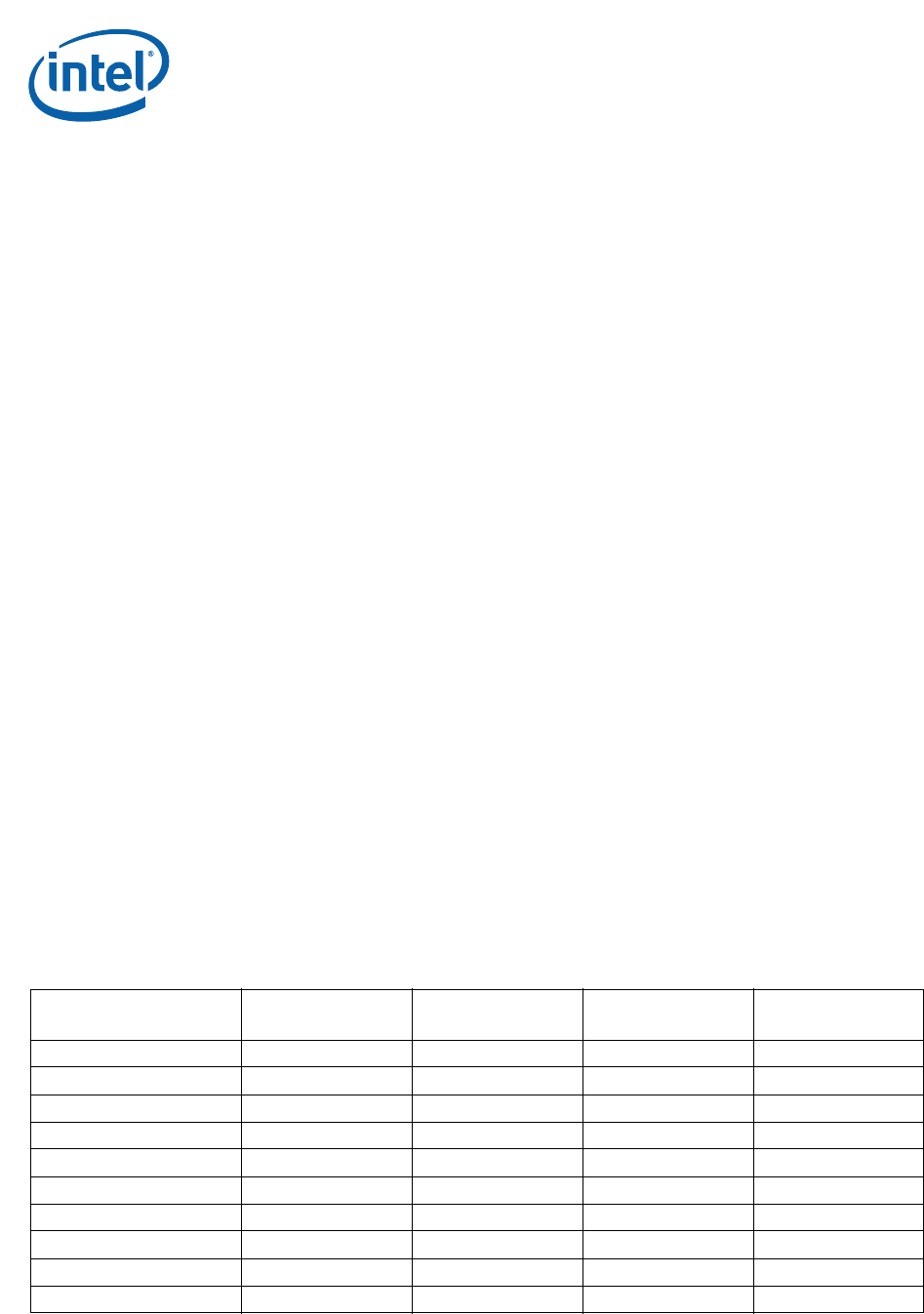

Table 100. PCI Byte Enables Using CRP Access Method

PCI_CRP_AD_CBE(23:20

)

PCI_CRP_WDATA

(31:24)

PCI_CRP_WDATA

(24:16)

PCI_CRP_WDATA

(15:8)

PCI_CRP_WDATA

(7:0)

0000 X X X X

0001 X X X

0010 X X X

0011 X X

0100 X X X

0101 X X

0110 X X

0111 X

1000 X X X

1001 X X