Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

262 Order Number: 252480-006US

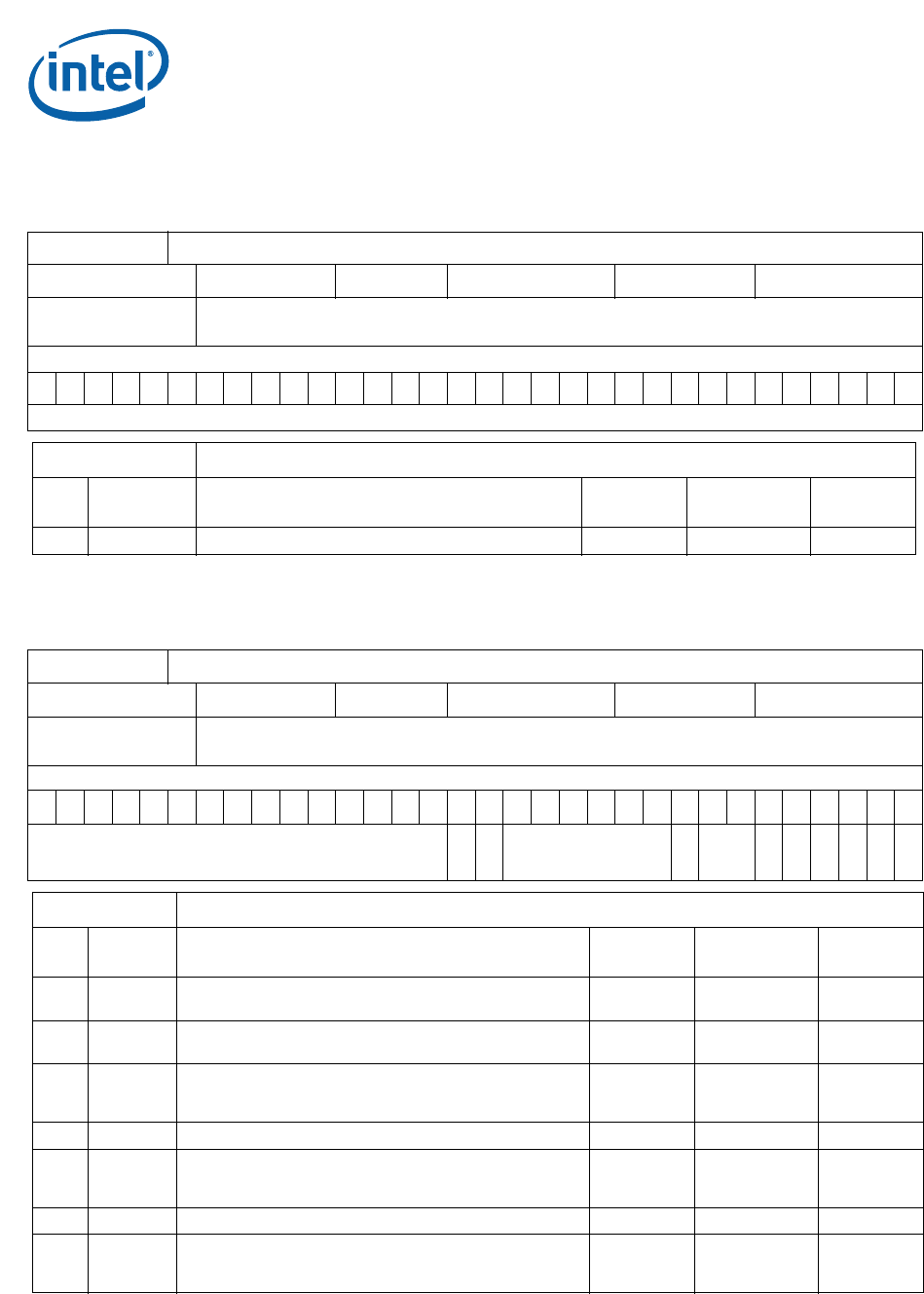

6.14.2.7 PCI Controller Configuration Port Read Data Register

(PCI_CRP_RDATA)

6.14.2.8 PCI Controller Control and Status Register

(PCI_CSR)

Register Name: PCI_CRP_RDATA

Hex Offset Address: 0xC0000018 Reset Hex Value: 0x00000000

Register

Description:

PCI configuration port read data register. Provides read data for CSR-initiated read accesses of the PCI

Controller PCI configuration registers in the PCI Core.

Access: See below.

31 0

CRP_RDATA

Register

PCI_CRP_RDATA

Bits Name Description

Reset

Value

PCI Access AHB Access

31:0 CRP_RDATA Read data for the configuration port read access. 0x00000000 RO RO

Register Name: PCI_CSR

Hex Offset Address: 0xC000001C Reset Hex Value: 0x0000000x

Register

Description:

Control and status for the PCI Controller.

Access: See below.

31 17161514 9876543210

(Reserved)

PRST

IC (Reserved)

ASE

(Rsvd)

DBT

ABE

PBS

ABS

ARBEN

HOST

Register PCI_CSR (Sheet 1 of 2)

Bits Name Description

Reset

Value

PCI Access AHB Access

31:1

7

(Reserved) – Read as 0 0x0000 RO RO

16 PRST

PCI Reset, When set to a 1, initializes the PCI controller

flip flops clocked by the PCI clock.

0x0 RO RW

15 IC

Initialization Complete. When at a logic 0 state, forces the

PCI Controller Target Interface to retry PCI cycles. When

set to a 1, PCI cycles will be accepted.

0RORW

14:9 (Reserved) – Read as 0 0x00 RO RO

8ASE

Assert System Error. When set to a 1, the PCI SERR#

output (PCI_SERR_N) will be asserted for 1 PCI clock

cycle if the pci_srcr.SER bit is set.

0RORW

7:6 (Reserved) – Read as 0 00 RO RO

5DBT

Doorbell Test mode enable. When set to a 1, the doorbell

registers pci_ahbdoorbell, pci_pcidoorbell become normal

read/write registers from the AHB bus.

0RORW