Intel

®

IXP42X product line and IXC1100 control plane processors—UTOPIA Level-2

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

540 Order Number: 252480-006US

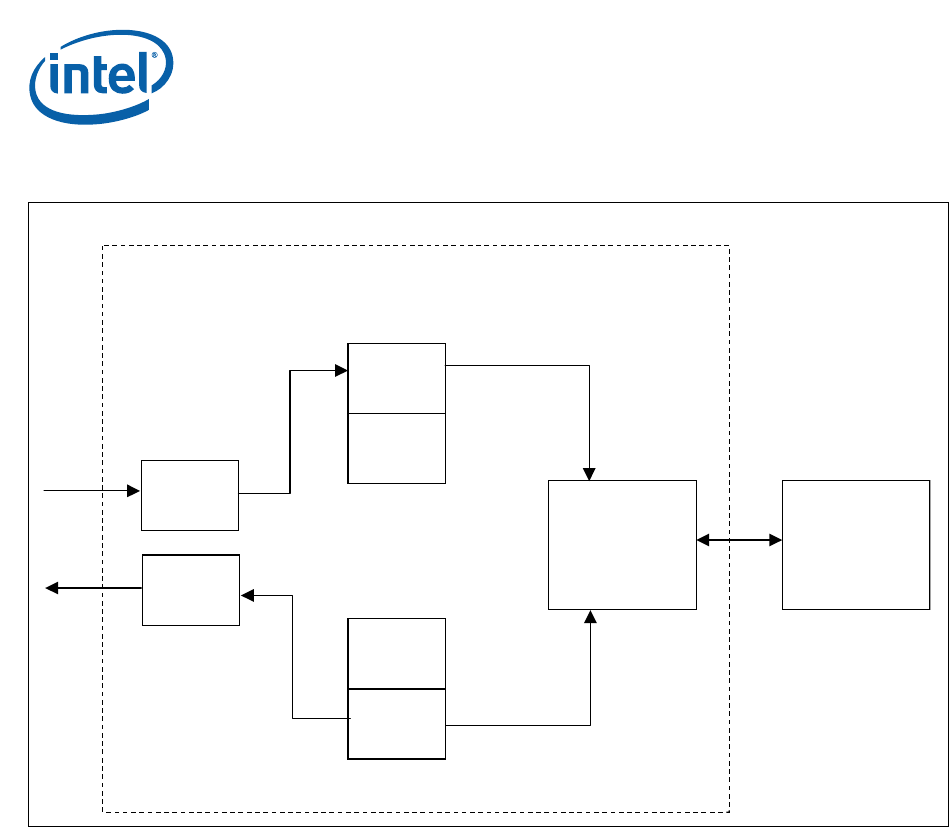

19.1 UTOPIA Transmit Module

The functionality supported by the Transmit Module is tightly coupled with the code

written on the Network Processor Engine. This section details the full hardware

capabilities of the Transmit Module contained within the UTOPIA Level-2 coprocessor of

the IXP42X product line and IXC1100 control plane processors. The module’s user-

accessible features are described in the Intel

®

IXP400 Software Programmer’s Guide

and may be a subset of the features described in this section.

The UTOPIA Level-2 Transmit interface transfers ATM cells to one or more UTOPIA-

compliant physical devices. In multiple-PHY (MPHY) mode, the UTOPIA Level-2 transmit

interface uses a round-robin polling routine to poll the various physical interfaces using

the five transmit address lines (UTP_TX_ADDR) to determine which physical interfaces

are ready to accept data transfers. The result of the polling is provided as status to the

Network Processor Engine.

The Transmit Module is the entity, within the UTOPIA coprocessor, that implements this

functionality. The Transmit Module will poll a programmable number of physical

interfaces as defined by the Transmit Address Range (TXADDRRANGE) register.

If five physical interfaces are connected to the UTOPIA Level-2 interface, a value of four

can be programmed into the Transmit Address Range (TXADDRRANGE) register by the

Network Processor Engine Core. The polling will always begin at logic address 0 and poll

sequentially to the value contained in the Transmit Address Range (TXADDRRANGE)

register.

Figure 97. UTOPIA Level-2 Coprocessor

Receive

Module

Transmit

Module

64-Byte

Receive

Buffer

64-Byte

Receive

Buffer

64-Byte

Transmit

Buffe

r

64-Byte

Transmit

Buffe

r

Network

Processor

Engine

Coprocessor

Interface

Network

Processor

Engine Core

2 Cell

Receive

FIFO

2 Cell

Transmit

FIFO

UTOPIA

Level 2

Receive

Interface

UTOPIA

Level 2

Transmit

Interface

UTOPIA Co

p

rocessor