Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 513

Universal Serial Bus (USB) v1.1 Device Controller—Intel

®

IXP42X product line and IXC1100

control plane processors

18.5.16.7 Receive FIFO Not Empty (RNE)

The receive FIFO not empty bit indicates that the receive FIFO has unread data in it.

When the UDCCS14[RPC] bit is set, this bit must be read to determine if there is any

data in the FIFO that Intel XScale

®

processor did not read.

The receive FIFO must continue to be read until this bit clears or data will be lost.

18.5.16.8 Receive Short Packet (RSP)

The receive short packet bit is used by the UDC to indicate that the received OUT

packet in the active buffer currently being read is a short packet or zero-sized packet.

This bit is updated by the UDC after the last byte is read from the active buffer and

reflects the status of the new active buffer.

If UDCCS14[RSP] is a 1 and UDCCS14[RNE] is a 0, it indicates a zero-length packet. If

a zero-length packet is present, the Intel XScale

®

processor must not read the data

register.

UDCCS14[RSP] clears when the next OUT packet is received.

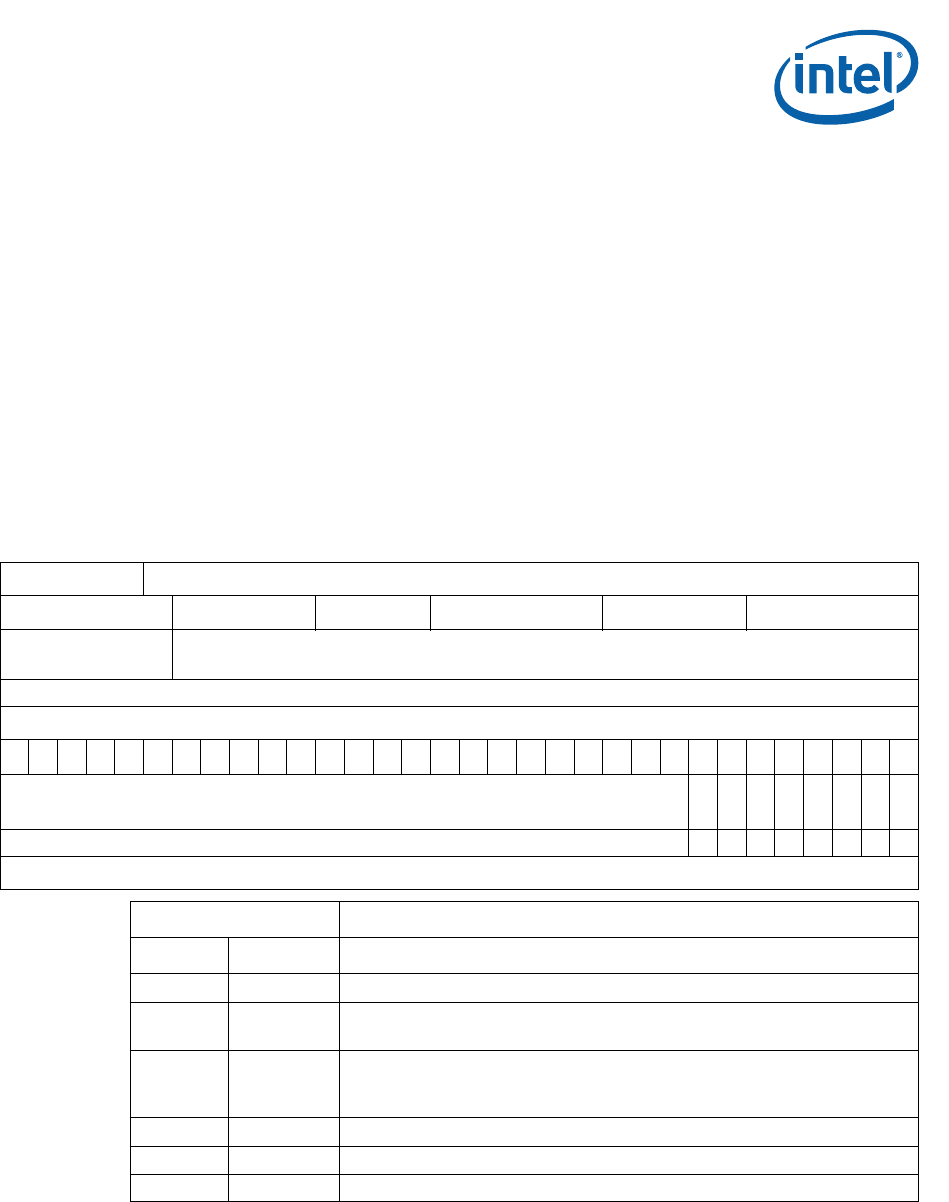

Register Name: UDCCS14

Hex Offset Address: 0x C800B048 Reset Hex Value: 0x00000000

Register

Description:

Universal Serial Bus Device Controller Endpoint 14 Control and Status Register

Access: Read/Write

Bits

31 876543210

(Reserved)

RSP

RNE

(Rsvd)

(Rsvd)

(Rsvd)

ROF

RPC

RFS

X 00000000

Resets (Above)

Register

UDCCS14 (Sheet 1 of 2)

Bits Name Description

31:8 Reserved for future use.

7RSP

Receive short packet (read only).

1 = Short packet received and ready for reading.

6RNE

Receive FIFO not empty (read-only).

0 = Receive FIFO empty.

1 = Receive FIFO not empty.

5 (Reserved). Always reads 0.

4 (Reserved). Always reads 0.

3(Reserved)