Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 155

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.8.3.4.2 Event Priority

The Intel XScale processor follows the exception priority specified in the ARM*

Architecture Reference Manual. The processor has additional exceptions that might be

generated while debugging. For information on these debug exceptions, see “Software

Debug” on page 88.

3.8.3.4.3 Prefetch Aborts

The Intel XScale processor detects three types of prefetch aborts: Instruction MMU

abort, external abort on an instruction access, and an instruction cache parity error.

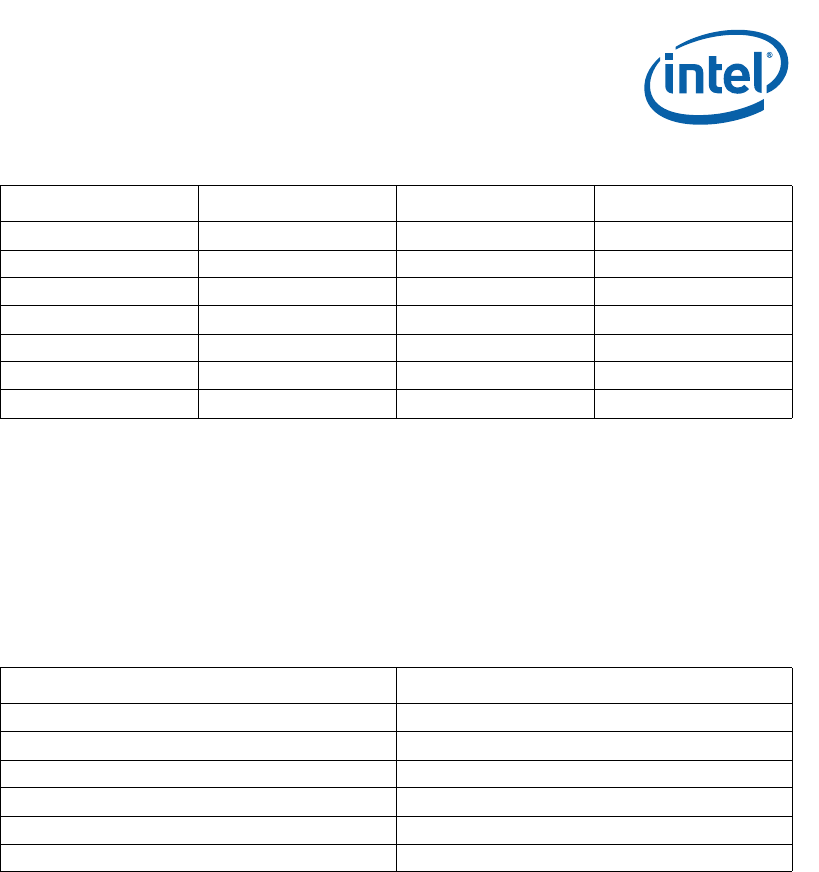

These aborts are described in Table 74.

When a prefetch abort occurs, hardware reports the highest priority one in the

extended Status field of the Fault Status Register. The value placed in R14_ABORT (the

link register in abort mode) is the address of the aborted instruction + 4.

Lock Abort Data Y N

MMU Data Data Y Y

External Data Data N N

Data Cache Parity Data N N

Software Interrupt Software Interrupt Y N

Undefined Instruction Undefined Instruction Y N

Debug Events

2

varies varies N

Table 72. Exception Summary (Sheet 2 of 2)

Exception Description Exception Type

1

Precise Updates FAR

Notes:

1. Exception types are those described in the ARM* Architecture Reference Manual.

2. Refer to “Software Debug” on page 88 for more details.

Table 73. Event Priority

Exception Priority

Reset 1 (Highest)

Data Abort (Precise & Imprecise) 2

FIQ 3

IRQ 4

Prefetch Abort 5

Undefined Instruction, SWI 6 (Lowest)