Intel

®

IXP42X product line and IXC1100 control plane processors—SDRAM Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

278 Order Number: 252480-006US

To remove the need for SDRAM refreshes to be implemented by the Intel XScale

processor, the SDRAM controller can be configured to perform automatic refreshes by

utilizing an internal refresh counter.

The SDRAM Controller is a target-only device residing on the AHB. A master residing on

the North AHB and the South AHB initiates every transaction on the SDRAM interface

via the SDRAM Controller. Whenever an AHB Master initiates a data transfer to an

address location mapped to the SDRAM memory access location, the SDRAM controller

responds by decoding the address and the AHB transfer type.

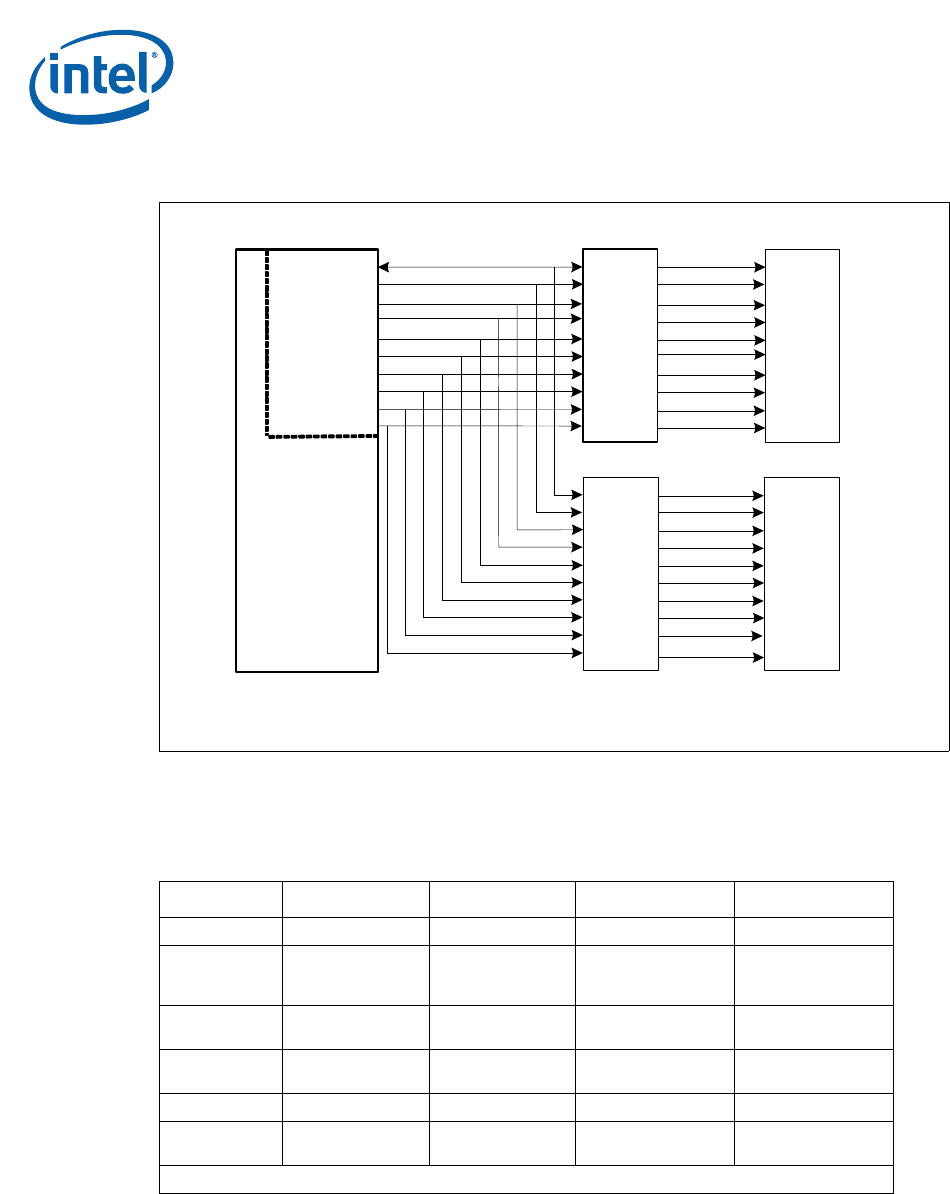

Figure 54. 64-, 128- or 256-Mbyte — Two-Bank SDRAM Interface Configuration

SDRAM Interface

SDM_DATA[31:0] DQ[15:0]

SDM_ADDR[12:0]

A[12:0]

SDM_CS[_N1:0]

SDM_RAS_N

SDM_CAS_N

SDM_WE_N

SDM__DQM[3:0]

SDM_BA[1:0]

SDM_CKE

SDM_CLKOUT

CS#

RAS#

CAS#

WE#

BA[1:0]

CKE

CLK

DQM[1:0]

DQ[15:0]

A[12:0]

CS#

RAS#

CAS#

WE#

BA[1:0]

CKE

CLK

DQM[1:0]

SDRAM#1

SDRAM#2

BANK0

DQ[15:0]

A[12:0]

CS#

RAS#

CAS#

WE#

BA[1:0]

CKE

CLK

DQM[1:0]

DQ[15:0]

A[12:0]

CS#

RAS#

CAS#

WE#

BA[1:0]

CKE

CLK

DQM[1:0]

SDRAM#1

SDM_CS_N0

DATA[15:0]

DATA[16:31]

SDRAM#2

SDM_CS_N1

SDM_CS_N1

DATA[15:0]

DATA[31:16]

BANK1

SDM_DQM[1:0]

SDM_DQM[3:2]

SDM_DQM[3:2]

SDM_DQM[3:0]

SDM_DQM[1:0]

B4964-01

Intel

®

IXP42X

Product Line /

Intel

®

IXC1100

Control Plane

Processor

Table 105. Supported Configuration of the SDRAM Controller

Total Memory 64 Mbit 128 Mbit 256 Mbit 512 Mbit

8 Mbyte One Chip 2M x 32

16 Mbyte

Two chips 4M x 16

or

two chips 2M x 32

32 Mbyte

Four chips 4M x

16

Two chips 8 M x

16

64 Mbyte

Four chips 8 M x

16

Two chips 16 M x 16

128 Mbyte Four chips 16 M x16 Two chips 32 M x 16

256 Mbyte

Four chips 32 M x

16

Note: 64-Mbit, 128-Mbit, 256-Mbit, and 512-Mbit columns refer to memory technologies.