Intel

®

IXP42X product line and IXC1100 control plane processors—General Purpose Input/

Output (GPIO)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

392 Order Number: 252480-006US

12.4.2 GPIO Output Enable Register

(GPOER)

Each pin’s output tristate buffer is controlled by programming this register. Each of the

16 bits in the register represents the control to the tristate buffer of the output pin.

12.4.3 GPIO Input Register

(GPINR)

This is a read-only register. This register contains the level of the I/O pin, either a 1 or

a 0.

Register GPOUTR

Bits Name Description

31:16 (Reserved). Reads back 0.

15 DO15

1 = Output a 1 on output pin, depends on GPCLKR24, GPOER15

0 = Output a 0 on output pin, depends on GPCLKR24, GPOER15

Reset: 0

14 DO14

1 = Output a 1 on output pin, depends on GPCLKR8, GPOER14

0 = Output a 0 on output pin, depends on GPCLKR8, GPOER14

Reset: 0

13:9 DO13:DO9

1 = Output a 1 on output pin, depends on GPOER[13:9]

0 = Output a 0 on output pin, depends on GPOER[13:9]

Reset: 0

8:0 DO8:DO0

1 = Output a 1 on output pin GPOER[8:0]

0 = Output a 0 on output pin GPOER[8:0]

Reset: 0

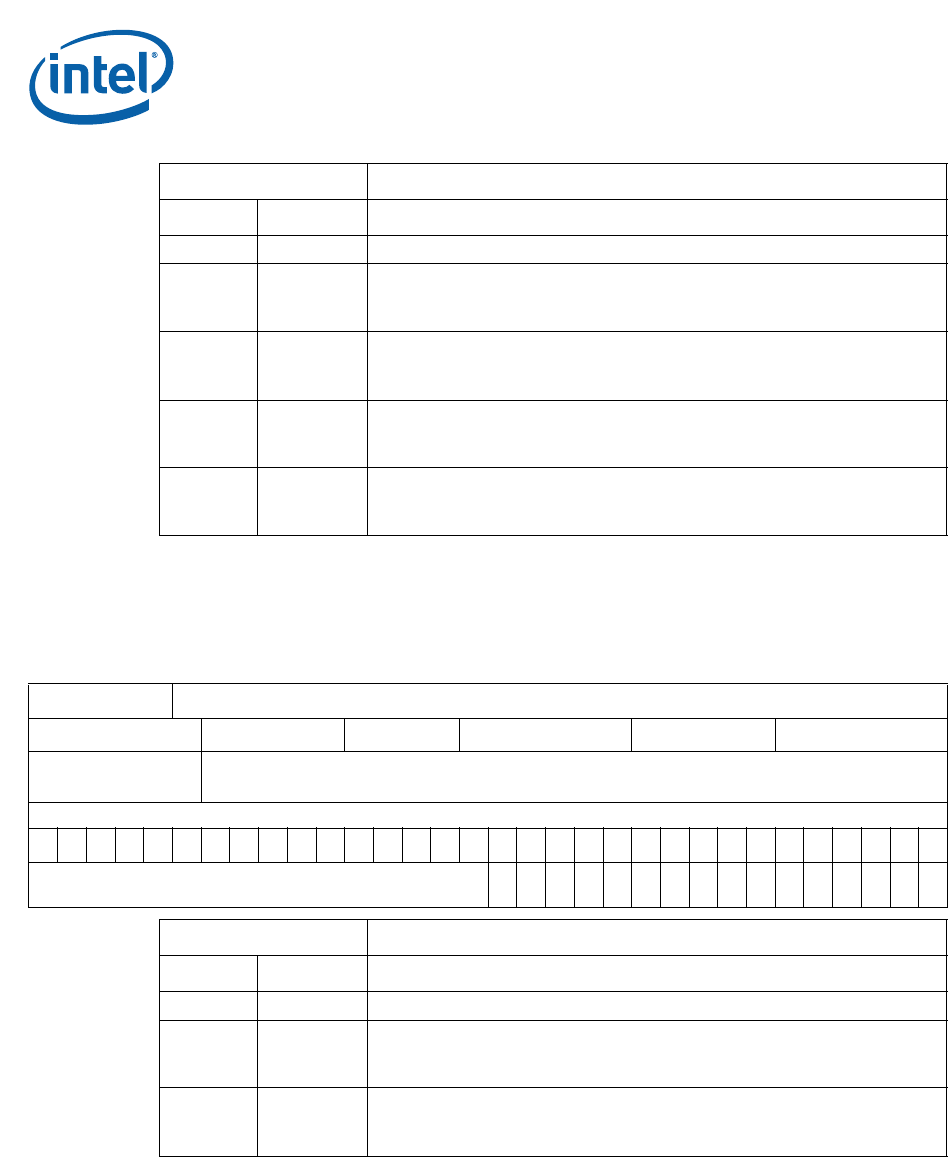

Register Name: GPOER

Hex Offset Address: 0xC800 4004 Reset Hex Value: 0x00007FFF

Register

Description:

I/O Output Enable register. Turns on output driver.

Access: Read/Write.

31 161514131211109876543210

(Reserved)

OE15

OE14

OE13

OE12

OE11

OE10

OE9

OE8

OE7

OE6

OE5

OE4

OE3

OE2

OE1

OE0

Register GPOER

Bits Name Description

31:16 (Reserved). Reads back 0.

15 OE15

1 = Output pin is tristated or input

0 = Output pin is driven

Reset: 0 (as clock is driven out on this pin during reset).

14:0 OE14:OE0

1 = Output pin is tristated or input

0 = Output pin is driven

Reset: 1