Intel

®

IXP42X product line and IXC1100 control plane processors—High-Speed Serial

Interfaces

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

460 Order Number: 252480-006US

By using the IxHssAcc API, the following settings should be considered when

configuring HSS interface for E1 operation:

• Frame size 256 bits (for E1).

• Frame sync simultaneous with first bit in first timeslot - TX frame offset and RX

frame offset should be set due to HSS logic, different values due to external device

can be accommodated.

• Select use of input/output TX/RX frame syncs.

• Select use of input/output clock, and clock speed.

• Select negative/positive clock for generating/sampling frame in transmit/receive.

• Select negative/positive clock for generating/sampling data in transmit/receive.

• Frame sync active level (high/low).

• MSb/LSb-first ordering for transmit and receive.

• Data polarity, maintain or invert.

• Select to not use FBit at frame start.

• Select value for idle timeslots on transmit and unused bit in 56k timeslots.

• Select buffer size.

• Configure lookup tables.

17.6.3 MVIP

MVIP provides a method of interlacing multiple E1 streams onto a single E1 line, and

multiple T1 streams onto a single T1 line. Increasing the clock speed and alternating

various timeslots helps provide this functionality. A single T1 line can also be mapped

into an E1 line.

By using the IxHssAcc API, the following settings should be considered when

configuring the HSS interface for MVIP:

• Set frame size for MVIP.

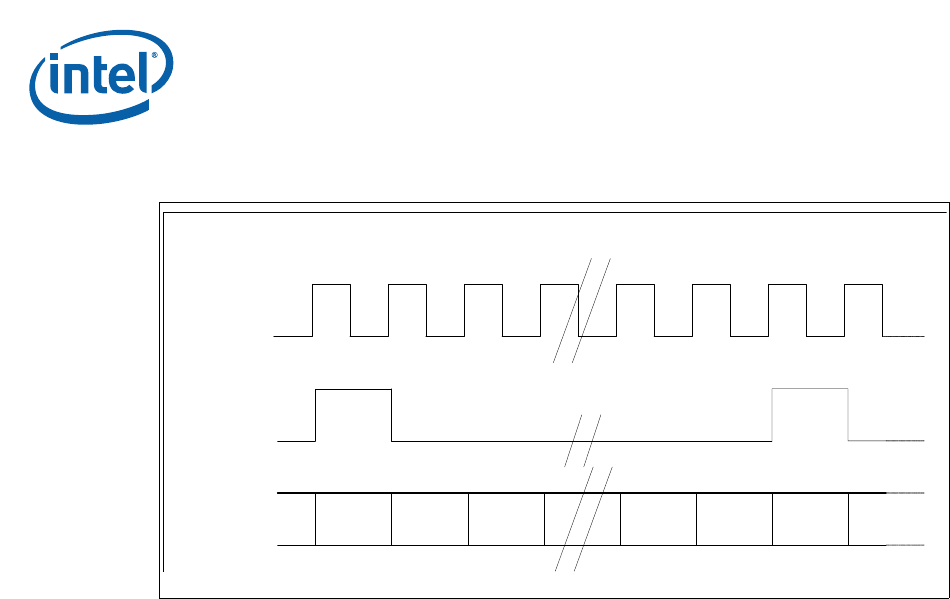

Figure 89. E1 Receive Frame

hss_rx_data

hss_rx_clock

hss_rx_frame

data1 data3 dat a2data1data256data2 data255