Intel

®

IXP42X product line and IXC1100 control plane processors—High-Speed Serial

Interfaces

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

458 Order Number: 252480-006US

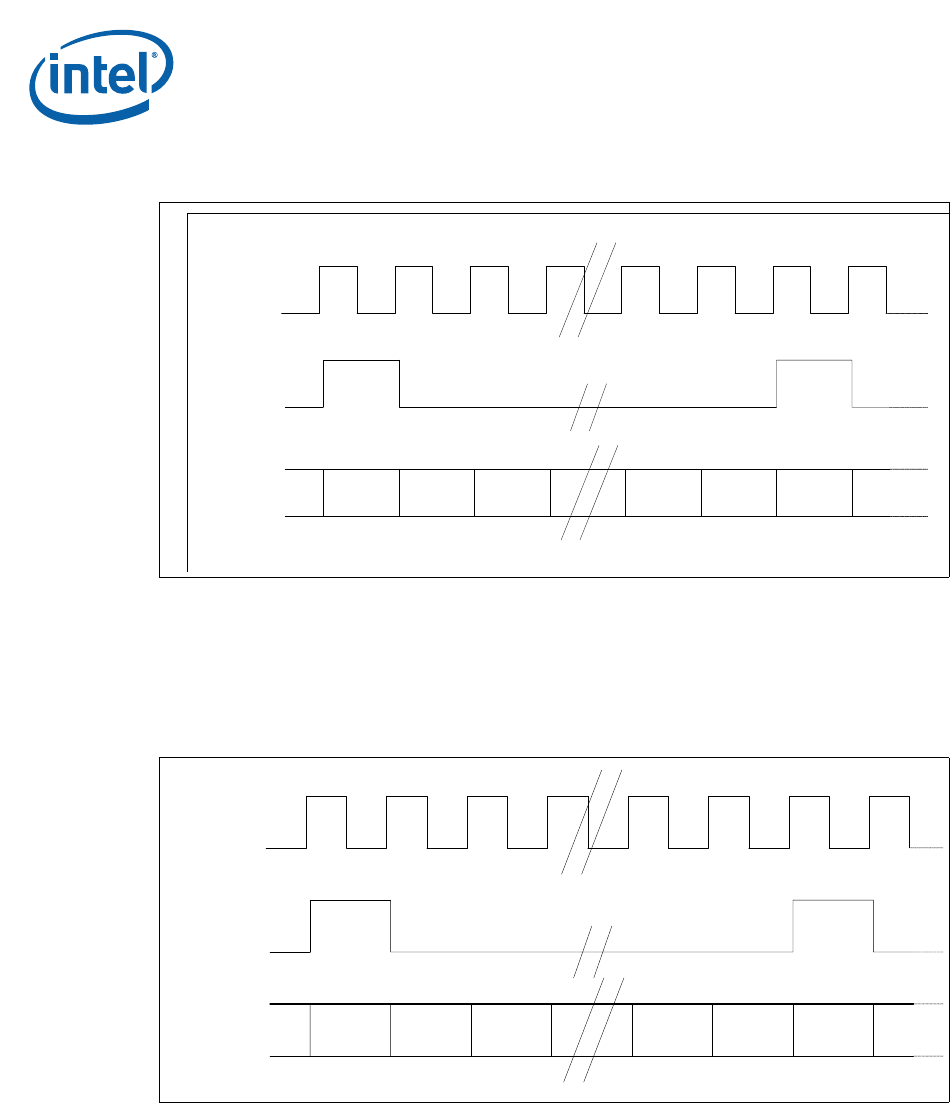

In Figure 86, the FBit to be transmitted is stored in the HSS Transmit FIFO. The HSS

knows which timeslot in the FIFO is holding the FBit, as it knows from the timeslot

counter and frame offset when the FBit should be transmitted.

In Figure 87, the FBit to be received is padded with 7 other bits (zeros) and placed into

the HSS Receive FIFO.

By using the IxHssAcc API, the following settings should be considered when

configuring HSS interface for T1 operation:

• Frame size 193 bits (for T1).

• Frame sync simultaneous with FBit - TX frame offset and RX frame offset should be

set due to HSS logic, different values due to external device can be accommodated.

• Select use of input/output TX/RX frame syncs.

• Select use of input/output clock, and clock speed.

• Select negative/positive clock for generating/sampling frame in transmit/receive.

• Select negative/positive clock for generating/sampling data in transmit/receive.

Figure 86. T1 Transmit Frame

hss_tx_data_out

hss_tx_clock

hss_tx_frame

FBit data1 data2 data 192data 191 FBit data1

Figure 87. T1 Receive Frame

hss_rx_data

hss_rx_clock

hss_rx_frame

FBit data1 data 192data 191 FBitdata2 data1