Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 109

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.6.11.6.5 DBG.RX

DBG.RX is written into the RX register based on the output of the RX Write Logic. Any

data that needs to be sent from the debugger to the processor must be loaded into

DBG.RX with DBG.V set to 1. DBG.RX is loaded from DBG_SR[34:3] when the JTAG

enters the Update_DR state.

DBG.RX is written to RX following an Update_DR when the RX Write Logic enables the

RX register.

3.6.11.6.6 DBG.D

DBG.D is provided for use during high speed download. This bit is written directly to

TXRXCTRL[29]. The debugger sets DBG.D when downloading a block of code or data to

IXP42X product line and IXC1100 control plane processors system memory. The debug

handler then uses TXRXCTRL[29] as a branch flag to determine the end of the loop.

Using DBG.D as a branch flags eliminates the need for a loop counter in the debug

handler code. This avoids the problem were the debugger’s loop counter is out of

synchronization with the debug handler’s counter because of overflow conditions that

may have occurred.

3.6.11.6.7 DBG.FLUSH

DBG.FLUSH allows the debugger to flush any previous data written to RX. Setting

DBG.FLUSH clears TXRXCTRL[31].

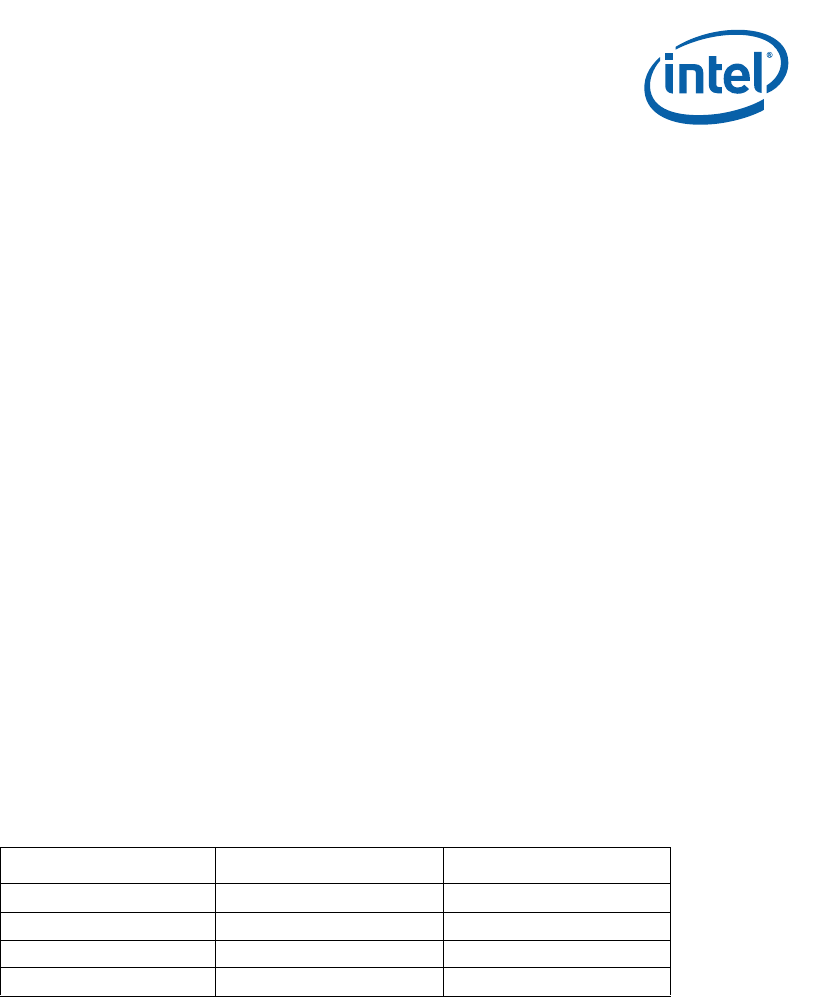

3.6.11.7 Debug JTAG Data Register Reset Values

Upon asserting TRST, the DEBUG data register is reset. Assertion of the reset pin does

not affect the DEBUG data register. Table 45 shows the reset and TRST values for the

data register. Note: these values apply for DBG_REG for SELDCSR, DBGTX and DBGRX.

3.6.12 Trace Buffer

The 256-entry trace buffer provides the ability to capture control flow information to be

used for debugging an application. Two modes are supported:

• The buffer fills up completely and generates a debug exception. Then SW empties

the buffer.

• The buffer fills up and wraps around until it is disabled. Then SW empties the

buffer.

3.6.12.1 Trace Buffer CP Registers

CP14 defines three registers (see Table 46) for use with the trace buffer. These CP14

registers are accessible using MRC, MCR, LDC and STC (CDP to any CP14 registers will

cause an undefined instruction trap). The CRn field specifies the number of the register

to access. The CRm, opcode_1, and opcode_2 fields are not used and should be set to

0.

Table 45. DEBUG Data Register Reset Values

Bit TRST RESET

DBG_REG[0] 0 unchanged

DBG_REG[1] 0 unchanged

DBG_REG[33:2] unpredictable unpredictable

DBG_REG[34] 0 unchanged