Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 515

Universal Serial Bus (USB) v1.1 Device Controller—Intel

®

IXP42X product line and IXC1100

control plane processors

18.5.17.5 Sent STALL (SST)

The sent stall bit is set by the UDC in response to FST successfully forcing a user-

induced STALL on the USB bus. This bit is not set if the UDC detects a protocol violation

from the host PC when a STALL handshake is returned automatically. In either event,

the Intel XScale

®

processor does not intervene and the UDC clears the STALL status

when the host sends a CLEAR_FEATURE command.

The endpoint operation continues normally and does not send another STALL condition,

even if the UDCCS15[SST] bit is set. To allow the software to continue to send the

STALL condition on the USB bus, the UDCCS15[FST] bit must be set again.

The Intel XScale

®

processor writes a 1 to the sent stall bit to clear it.

18.5.17.6 Force STALL (FST)

The Intel XScale

®

processor can set the force stall bit to force the UDC to issue a STALL

handshake to all IN tokens. STALL handshakes continue to be sent until the Intel

XScale

®

processor clears this bit by sending a Clear Feature command.

The UDCCS15[SST] bit is set when the STALL state is actually entered, but this may be

delayed if the UDC is active when the UDCCS15[FST] bit is set. The UDCCS15[FST] bit

is automatically cleared when the UDCCS15[SST] bit is set.

To ensure that no data is transmitted after the Clear Feature command is sent and the

host resumes IN requests, software must clear the transmit FIFO by setting the

UDCCS15[FTF] bit.

18.5.17.7 Bit 6 Reserved

Bit 6 is reserved for future use.

18.5.17.8 Transmit Short Packet (TSP)

Software uses the transmit short to indicate that the last byte of a data transfer has

been sent to the FIFO. This indicates to the UDC that a short packet or zero-sized

packet is ready to transmit. Software must not set this bit if a packet of 8 bytes is to be

transmitted.

When the data packet is successfully transmitted, the UDC clears this bit.

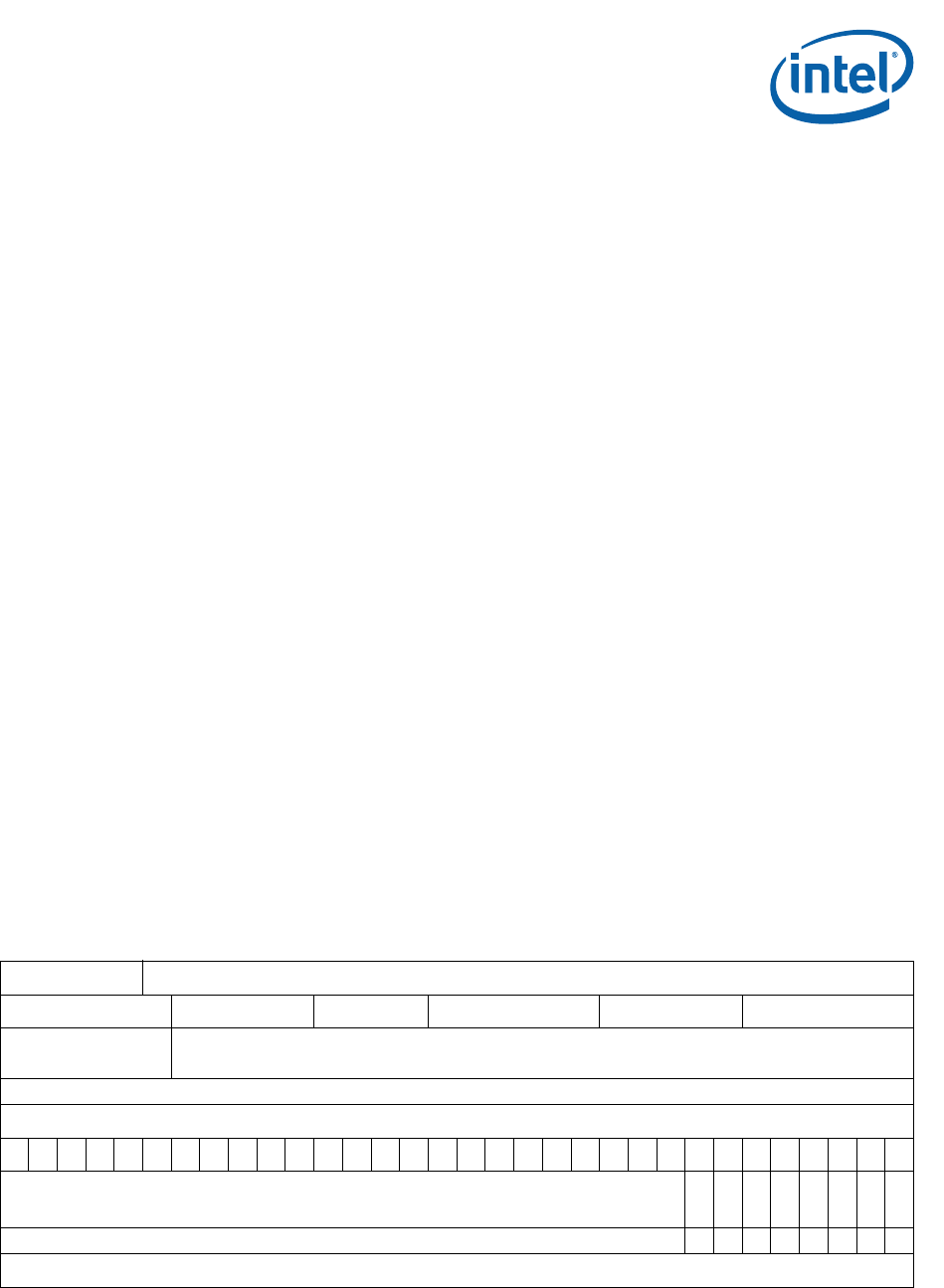

Register Name: UDCCS15

Hex Offset Address: 0x C800B04C Reset Hex Value: 0x00000001

Register

Description:

Universal Serial Bus Device Controller Endpoint 15 Control and Status Register

Access: Read/Write

Bits

31 876543210

(Reserved)

TSP

(Rsvd)

FST

SST

TUR

FTF

TPC

TFS

X 00000001

Resets (Above)