Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

88 Order Number: 252480-006US

3.5.2.3 Software Debug Registers

Software debug is supported by address breakpoint registers (Coprocessor 15,

register 14), serial communication over the JTAG interface and a trace buffer.

Registers 8 and 9 are used for the serial interface and registers 10 through 13 support

a 256 entry trace buffer. Register 14 and 15 are the debug link register and debug

SPSR (saved program status register). These registers are explained in more detail in

“Software Debug” on page 88.

Opcode_2 and CRm should be zero.

3.6 Software Debug

This section describes the software debug and related features implemented in the

IXP42X product line and IXC1100 control plane processors, namely:

• Debug modes, registers and exceptions

• A serial debug communication link via the JTAG interface

•A trace buffer

• A mechanism to load the instruction cache through JTAG

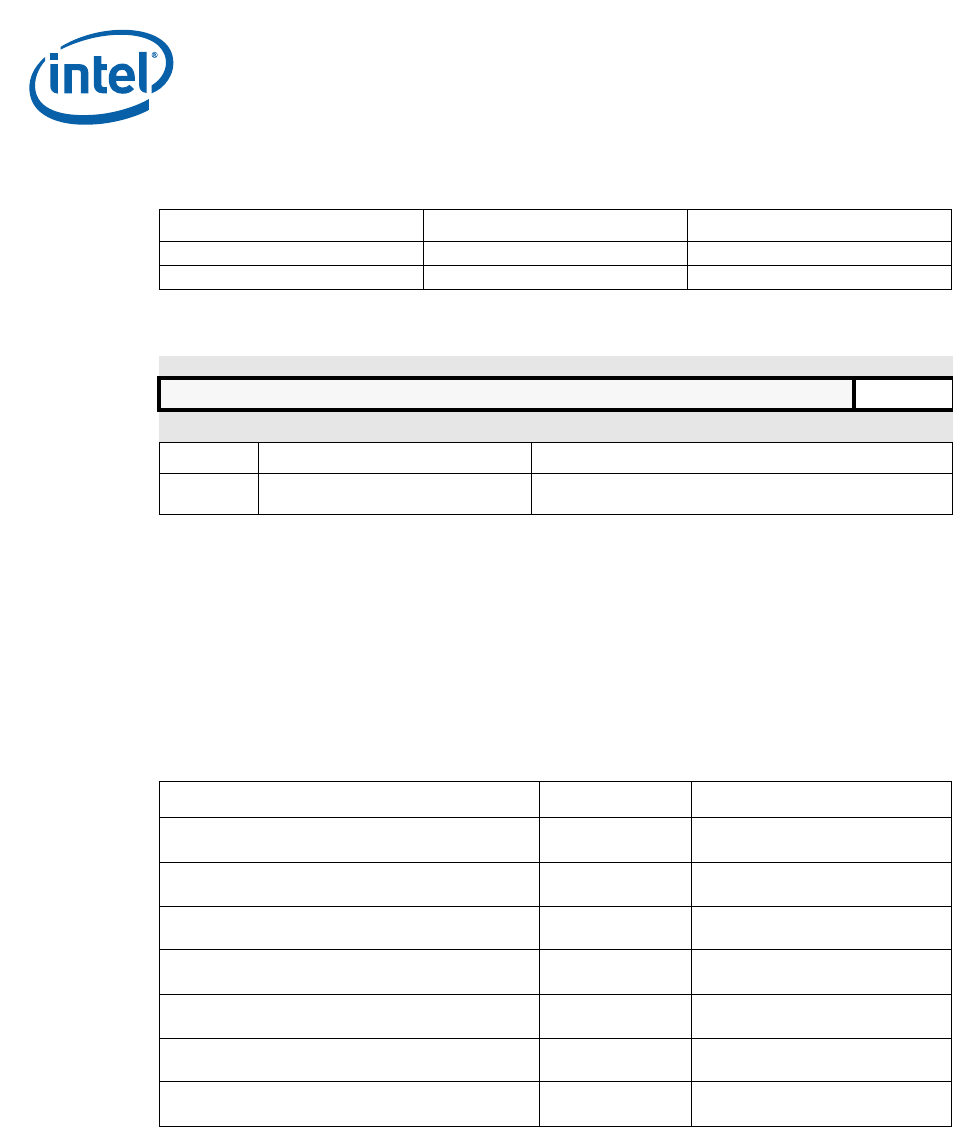

Table 30. Clock and Power Management

Function Data Instruction

Read CCLKCFG ignored MRC p14, 0, Rd, c6, c0, 0

Write CCLKCFG CCLKCFG value MCR p14, 0, Rd, c6, c0, 0

Table 31. CCLKCFG Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CCLKCFG

reset value: unpredictable

Bits Access Description

31:0

Read-unpredictable / Write-as-Zero

always

Reserved (write as zero)

Table 32. Accessing the Debug Registers

Function CRn (Register #) Instruction

Access Transmit Debug Register (TX) 0b1000

MRC p14, 0, Rd, c8, c0, 0

MCR p14, 0, Rd, c8, c0, 0

Access Receive Debug Register (RX) 0b1001

MCR p14, 0, Rd, c9, c0, 0

MRC p14, 0, Rd, c9, c0, 0

Access Debug Control and Status Register

(DBGCSR)

0b1010

MCR p14, 0, Rd, c10, c0, 0

MRC p14, 0, Rd, c10, c0, 0

Access Trace Buffer Register (TBREG) 0b1011

MCR p14, 0, Rd, c11, c0, 0

MRC p14, 0, Rd, c11, c0, 0

Access Checkpoint 0 Register (CHKPT0) 0b1100

MCR p14, 0, Rd, c12, c0, 0

MRC p14, 0, Rd, c12, c0, 0

Access Checkpoint 1 Register (CHKPT1) 0b1101

MCR p14, 0, Rd, c13, c0, 0

MRC p14, 0, Rd, c13, c0, 0

Access Transmit and Receive Debug Control

Register

0b1110

MCR p14, 0, Rd, c14, c0, 0

MRC p14, 0, Rd, c14, c0, 0