Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 123

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.6.14.5 Dynamically Loading IC After Reset

An external host can load code into the instruction cache “on the fly” or “dynamically.”

This occurs when the host downloads code while the processor is not being reset.

However, this requires strict synchronization between the code running on the IXP42X

product line and IXC1100 control plane processors and the external host. The

guidelines for downloading code during program execution must be followed to ensure

proper operation of the processor. The description in this section focuses on using a

debug handler running on the IXP42X product line and IXC1100 control plane

processors to synchronize with the external host, but the details apply for any

application that is running while code is dynamically downloaded.

To dynamically download code during software debug, there must be a minimal debug

handler stub, responsible for doing the handshaking with the host, resident in the

instruction cache. This debug handler stub should be downloaded into the instruction

cache during processor reset using the method described in “Loading IC During Reset”

on page 119. “Dynamic Code Download Synchronization” on page 124 describes the

details for implementing the handshaking in the debug handler.

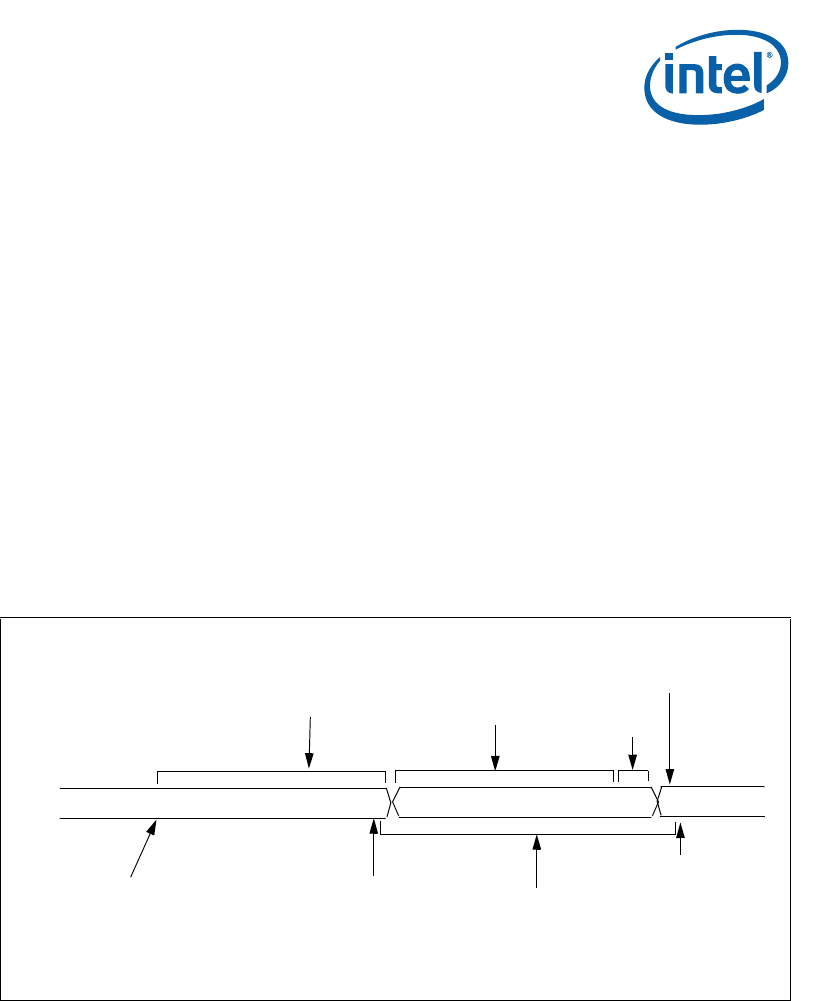

Figure 28 shows a high level view of the actions taken by the host and debug handler

during dynamic code download.

The following steps describe the details for downloading code:

• Since the debug handler is responsible for synchronization during the code

download, the handler must be executing before the host can begin the download.

The debug handler execution starts when the application running on the IXP42X

product line and IXC1100 control plane processors generate a debug exception or

when the host generates an external debug break.

• While the DBGTX JTAG instruction is in the JTAG IR (see “DBGTX JTAG Command”

on page 105), the host polls DBG_SR[0], waiting for the debug handler to set it.

• When the debug handler gets to the point where it is OK to begin the code

download, it writes to TX, which automatically sets DBG_SR[0]. This signals the

host it is OK to begin the download. The debug handler then begins polling

TXRXCTRL[31] waiting for the host to clear it through the DBGRX JTAG register (to

indicate the download is complete).

• The host writes LDIC to the JTAG IR, and downloads the code. For each line

downloaded, the host must invalidate the target line before downloading code to

Figure 28. Downloading Code in IC During Program Execution

DBGRX

JTAG IR

DBGTX

LDIC

wait for handler to signal

download code

signal handler

Handler begins execution

signal host ready

wait for host to signal

download is complete

continue execution.

ready to start download

for download

download complete

Debugger Actions

Debug Handler Actions

clock

15 TCKs