Intel

®

IXP42X product line and IXC1100 control plane processors—UTOPIA Level-2

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

538 Order Number: 252480-006US

19.0 UTOPIA Level-2

The functionality supported by the UTOPIA Level-2 interface is tightly coupled with the

code written on the Network Processor Engine (NPE). This chapter details the full

hardware capabilities of the UTOPIA-2 interface contained within the UTOPIA Level-2

coprocessor of the Intel

®

IXP42X Product Line of Network Processors and IXC1100

Control Plane Processor. The features accessible by the user are described in the Intel

®

IXP400 Software Programmer’s Guide and may be a subset of the features described in

this chapter.

Not all of the Intel

®

IXP42X product line and IXC1100 control plane processors have

this functionality. See Table 173.

The UTOPIA Level-2 is an industry-standard interface that is used to provide connection

between Asynchronous Transmission Mode (ATM) and physical layer (PHY) of an ATM

network. The UTOPIA-2 coprocessor is the entity, within the IXP42X product line and

IXC1100 control plane processors, that provides the UTOPIA Level-2 interface.

The UTOPIA Level-2 coprocessor, implemented on the IXP42X product line and IXC1100

control plane processors, provides an 8-bit, UTOPIA Level-2 interface operating at

speeds of up to 33 MHz. The UTOPIA Level-2 interface can be configured to operate in

a single-PHY (SPHY) or a multiple-PHY (MPHY) environment.

The interface contains five transmit and five receive address lines for multi-PHY

selection. The UTOPIA Level-2 coprocessor is comprised of three functional modules:

• UTOPIA Transmit Module

• UTOPIA Receive Module

• Network Processor Engine (NPE) Core Interface Module

Two 128-byte-deep FIFOs are contained in each direction of data flow — one FIFO for

transmit and one FIFO for receive. Each FIFO is organized into two cell buffers, each

being 64 bytes deep. This FIFO arrangement allows the receive module to be

processing a cell and storing it away at the same time the Network Processor Engine

core is processing a previously received cell.

In the transmit direction, the Network Processor Engine core can be placing a cell into

one transmit buffer while the Transmit Module is removing the cell from the other

transmit buffer.

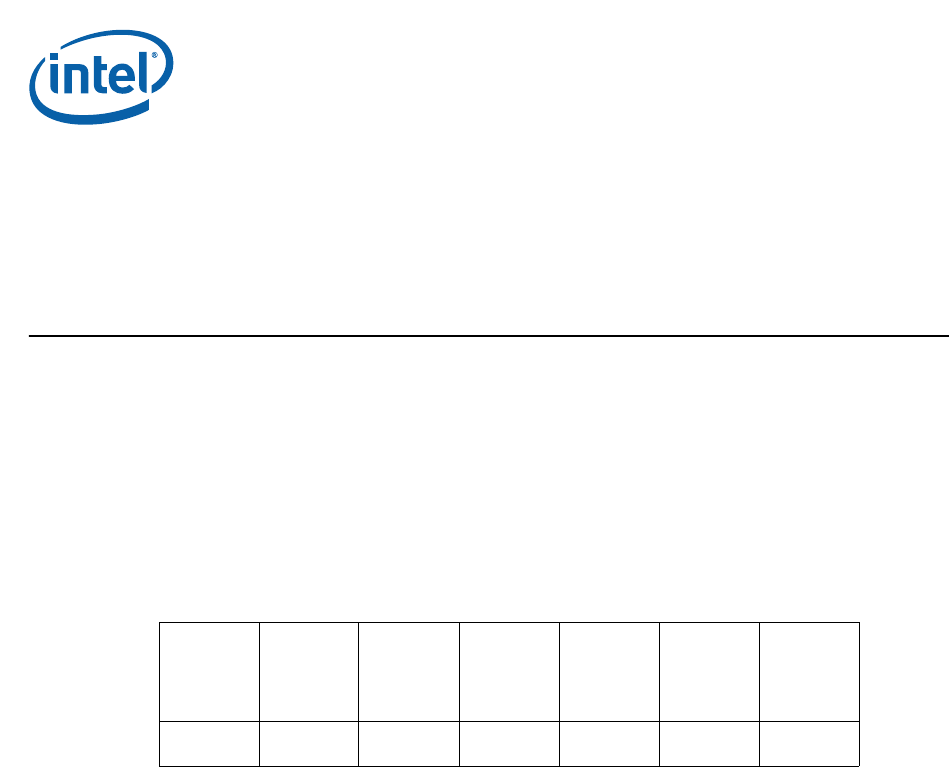

Table 173. Processors’ Devices with UTOPIA

Intel

®

IXP425

Network

Processor

B Step

Intel

®

IXP423

Network

Processor

Intel

®

IXP422

Network

Processor

Intel

®

IXP421

Network

Processor

Intel

®

IXP420

Network

Processor

Intel

®

IXC1100

Control

Plane

Processor

UTOPIA

Level-2

XX X