Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 395

General Purpose Input/Output (GPIO)—Intel

®

IXP42X product line and IXC1100 control plane

processors

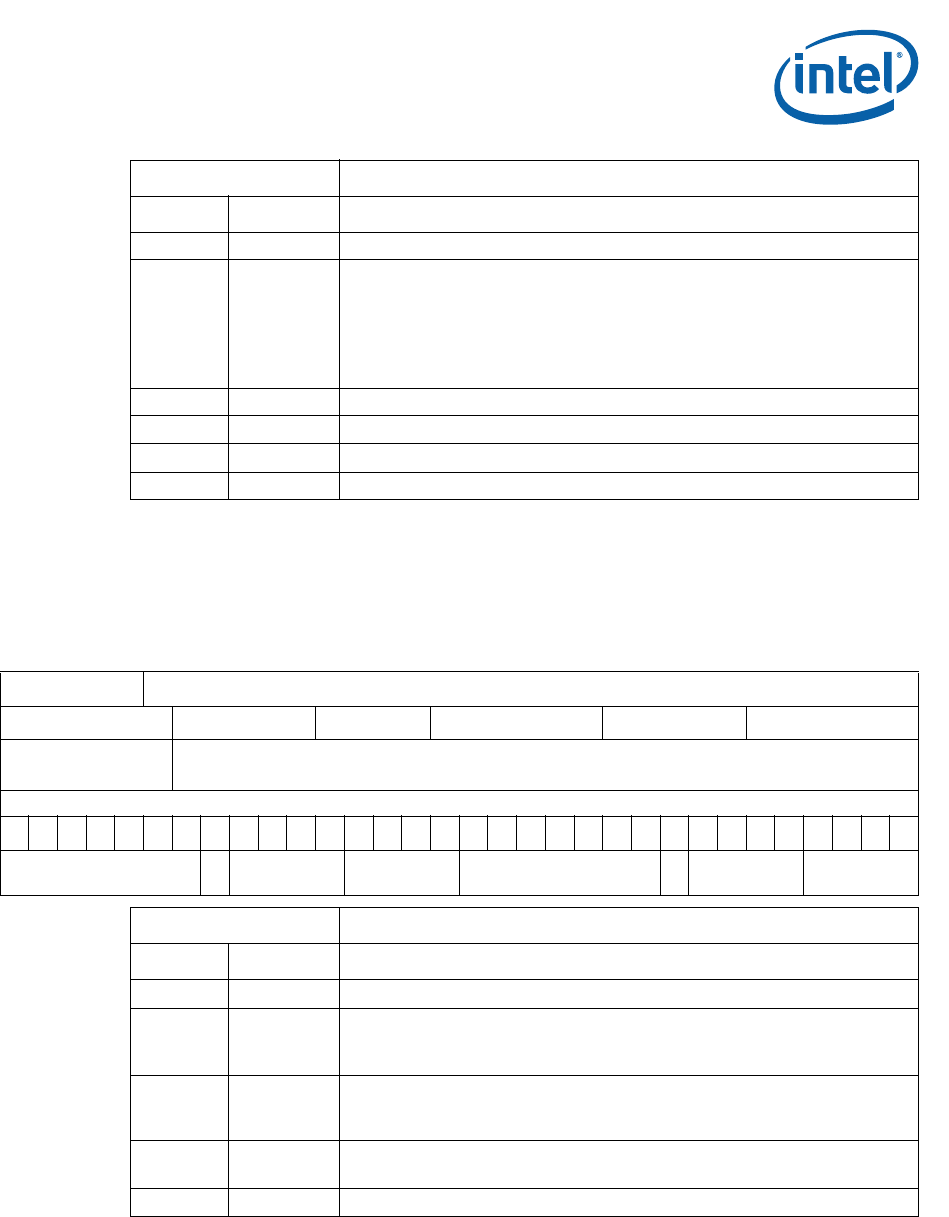

12.4.7 GPIO Clock Register

(GPCLKR)

This register controls the use of GPIO15 and GPIO14 as clock outputs. GPOER defines

the output enable for the driver; this register controls both the clock dividers and a

MUX between the clock data and the data defined in GPOUTR.

17:15 GPIO13 Not used.

14:12 GPIO12

000 = Active High

001 = Active Low

010 = Rising Edge

011 = Falling Edge

1xx = Transitional

Resets to 000 – Active High

11:9 GPIO11 As per GPIO12

8:6 GPIO10 As per GPIO12

5:3 GPIO9 As per GPIO12

2:0 GPIO8 As per GPIO12

Register

GPIT2R (Sheet 2 of 2)

Bits Name Description

Register Name: GPCLKR

Hex Offset Address: 0xC800 4018 Reset Hex Value: 0x01100000

Register

Description:

This register controls the use of GPIO 15 and GPIO14 as clock sources.

Access: See below.

31 25 24 23 20 19 16 15 9 8 7 4 3 0

(Reserved)

Mx15

CLK1TC CLK1DC (Reserved)

Mx14

CLK0TC CLK0DC

Register

GPCLKR (Sheet 1 of 2)

Bits Name Description

31:25 Not used. Ignored on writes and driven logic 0 on reads.

24 MUX15

0 = Control from GPOUTR Register

1 = Clock output

Reset: 1

23:20 CLK1TC

Terminal count for a 4 bit up counter @ PCLK. An F in this field and the CLK1DC

field is a special case to provide PCLK/2.

Reset: 0x1

19:16 CLK1DC

Represents the number of counts for which clock output should be low.

Reset: 0x0

15:9 - Not used. Ignored on writes and driven logic 0 on reads.