Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 47

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.1.1.2.4 Memory Operation Ordering

A fence memory operation (memop) is one that guarantees all memops issued prior to

the fence will execute before any memop issued after the fence. Thus software may

issue a fence to impose a partial ordering on memory accesses.

Table 5 on page 47 shows the circumstances in which memops act as fences.

Any swap (SWP or SWPB) to a page that would create a fence on a load or store is a

fence.

3.1.1.2.5 Exceptions

The MMU may generate prefetch aborts for instruction accesses and data aborts for

data memory accesses. The types and priorities of these exceptions are described in

“Event Architecture” on page 154.

Data address alignment checking is enabled by setting bit 1 of the Control Register

(CP15, register 1). Alignment faults are still reported even if the MMU is disabled. All

other MMU exceptions are disabled when the MMU is disabled.

3.1.2 Interaction of the MMU, Instruction Cache, and Data Cache

The MMU, instruction cache, and data/mini-data cache may be enabled/disabled

independently. The instruction cache can be enabled with the MMU enabled or disabled.

However, the data cache can only be enabled when the MMU is enabled. Therefore only

three of the four combinations of the MMU and data/mini-data cache enables are valid.

The invalid combination will cause undefined results.

Table 4. Data Cache and Buffer Behavior When X = 1

C B Cacheable Bufferable Write Policy

Line

Allocation

Policy

Notes

0 0 - - - - Unpredictable -- do not use

01 N Y - -

Writes will not coalesce into

buffers

1

10

(Mini Data

Cache)

---

Cache policy is determined

by MD field of Auxiliary

Control register

2

11 Y Y Write Back

Read/Write

Allocate

Notes:

1. Normally, bufferable writes can coalesce with previously buffered data in the same address range.

2. See “Register 1: Control and Auxiliary Control Registers” on page 77 for a description of this register.

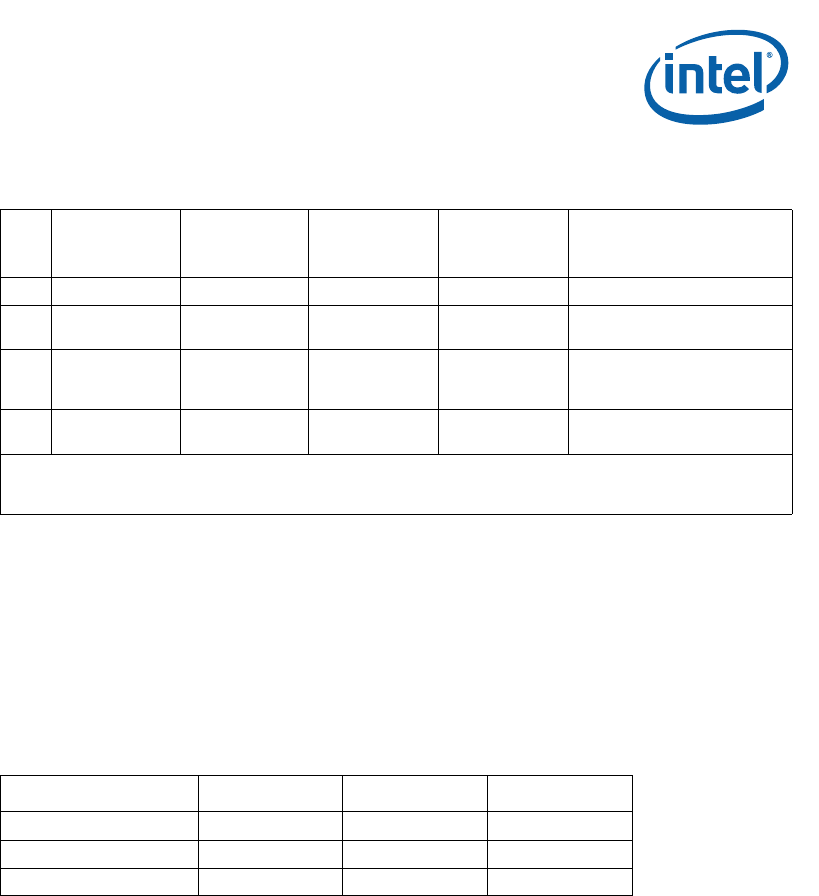

Table 5. Memory Operations that Impose a Fence

Operation X C B

load - 0 -

store 1 0 1

load or store 0 0 0