Intel

®

IXP42X product line and IXC1100 control plane processors—Expansion Bus Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

322 Order Number: 252480-006US

8.9.9 Configuration Register 0

At power up or whenever a reset is asserted, the expansion-bus address outputs are

switched to inputs and the states of the bits are captured and stored in Configuration

Register 0, bits 23 through 0. This occurs on the first cycle after the synchronous de-

assertion of the reset signal.

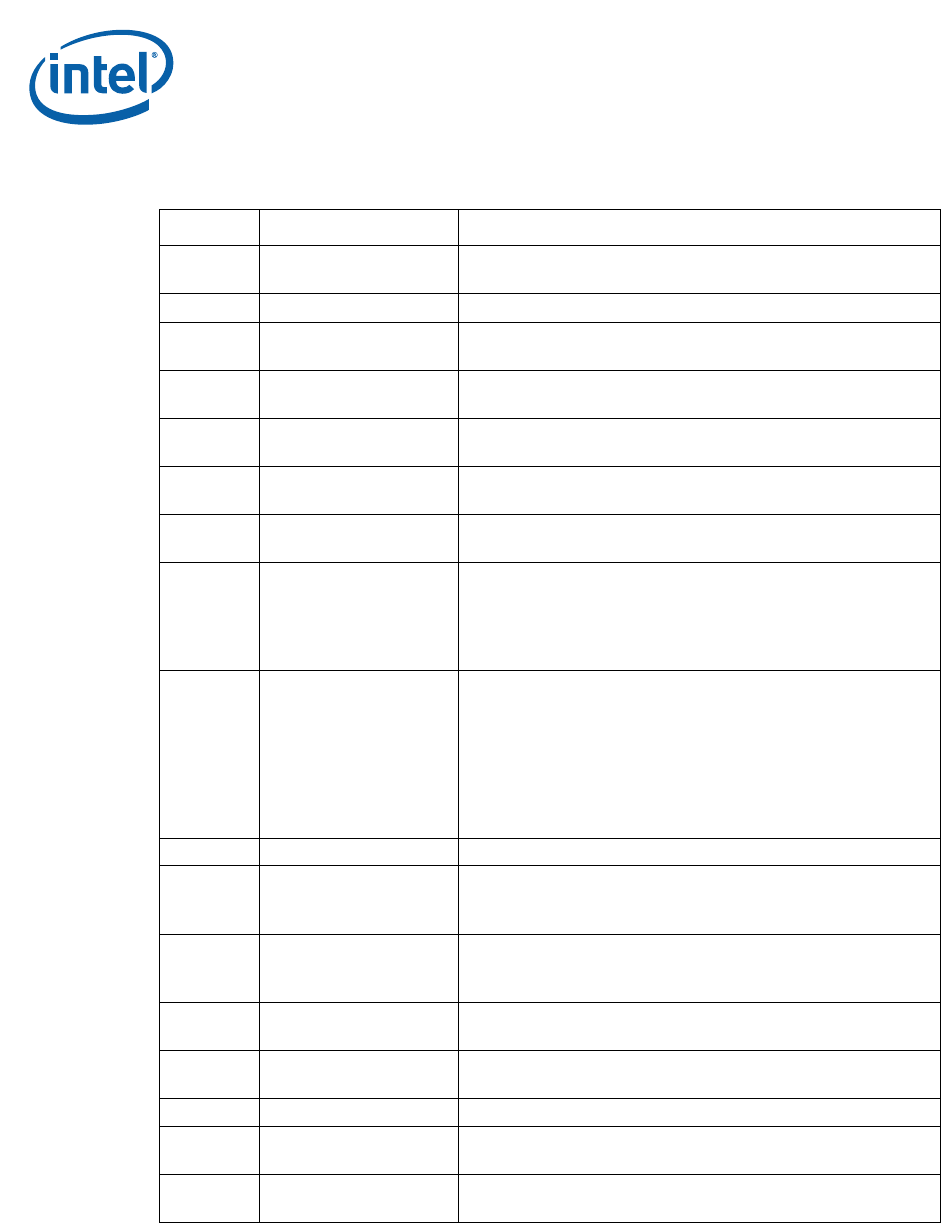

Table 123. Bit Level Definition for each of the Timing and Control Registers

Bits Name Description

31 CSx_EN

0 = Chip Select x disabled

1 = Chip Select x enabled

30 (Reserved)

29:28 T1 – Address timing

00 = Generate normal address phase timing

01 - 11 = Extend address phase by 1 - 3 clocks

27:26

T2 – Setup / Chip Select

Timing

00 = Generate normal setup phase timing

01 - 11 = Extend setup phase by 1 - 3 clocks

25:22 T3 – Strobe Timing

0000 = Generate normal strobe phase timing

0001-1111 = Extend strobe phase by 1 - 15 clocks

21:20 T4 – Hold Timing

00 = Generate normal hold phase timing

01 - 11 = Extend hold phase by 1 - 3 clocks

19:16 T5 – Recovery Timing

0000 = Generate normal recovery phase timing

0001-1111 = Extend recovery phase by 1 - 15 clocks

15:14 CYC_TYPE

00 = Configures the expansion bus for Intel cycles.

01 = Configures the expansion bus for Motorola* cycles.

10 = Configures the expansion bus for HPI cycles.

(HPI reserved for chip selects [7:4] only)

11 = Reserved

13:10 CNFG[3:0]

Device Configuration Size. Calculated using the formula:

SIZE OF ADDR SPACE = 2

(9+CNFG[3:0])

For Example:

0000 = Address space of 2

9

= 512 Bytes

…

1000 = Address space of 2

17

= 128 Kbytes

…

1111 = Address space of 2

24

= 16 Mbytes

9:7 (Reserved)

6BYTE_RD16

Byte read access to Half Word device

0 = Byte access disabled.

1 = Byte access enabled.

5HRDY_POL

HPI HRDY polarity (reserved for exp_cs_n[7:4] only)

0 = Polarity low true.

1 = Polarity high true.

4MUX_EN

0 = Separate address and data buses.

1 = Multiplexed address / data on data bus.

3SPLT_EN

0 = AHB split transfers disabled.

1 = AHB split transfers enabled.

2(Reserved)

1WR_EN

0 = Writes to CS region are disabled.

1 = Writes to CS region are enabled.

0BYTE_EN

0 = Expansion bus uses 16-bit-wide data bus.

1 = Expansion bus uses only 8-bit data bus.