Intel

®

IXP42X product line and IXC1100 control plane processors—AHB Queue Manager (AQM)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

568 Order Number: 252480-006US

§ §

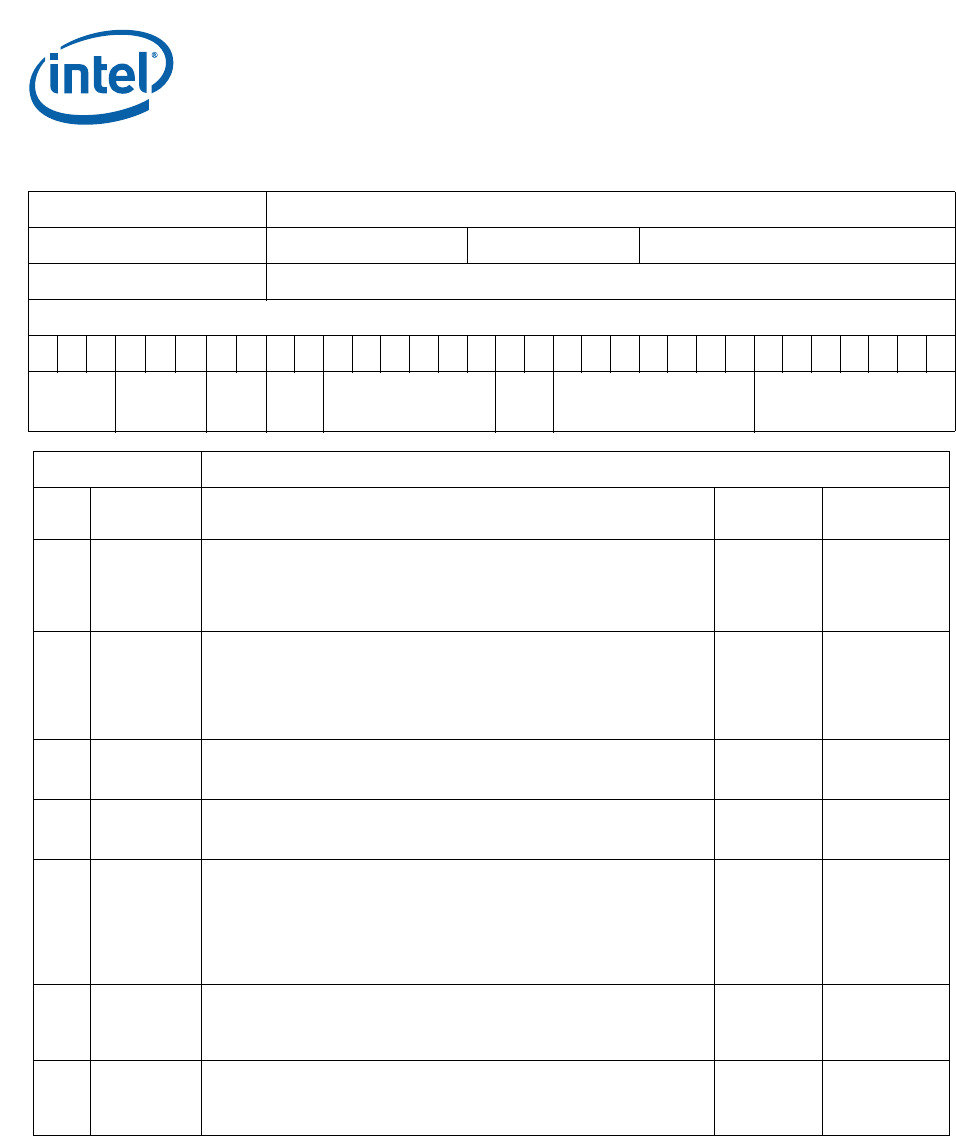

Register Name: QUECONFIG (0 <= n <=63)

Physical Address:

Queue #n 0x(2000 + 4n)

Reset Hex Value: 0xUUUUUUUU

Register Description: Queue #n configuration word located in SRAM.

Access:

31 24 23 16 15 8 7 0

Queue (n)

NF

Watermark

Queue (n)

NE

Watermark

Q (n)

Buffer

Size

Q (n)

Entry

Size

Queue (n) Base

Address

Res. Queue (n) Read Pointer Queue (n) Write Pointer

Register QUECONFIG (0 <= n <=63)

Bits Name Description

Reset

Value

Access

31:2

9

Nearly Full

Watermark

The Nearly Full Watermark can be configured via these bits. The

Nearly Full Watermark can be set in the range 0 (“000”), 1 (“001”), 2

(“010”), 04(“011”), 8 (“100”), 16 (“101”), 32 (“110”), or 64 (“111”)

entries from the top of the queue. The usable range for the Nearly Full

Watermark selection is limited to a value less than the buffer size.

UR/W

28:2

6

Nearly Empty

Watermark

The Nearly Empty Watermark can be configured via these bits. The

Nearly Empty Watermark can be set in the range 0 (“000”), 1 (“001”),

2 (“010”), 04(“011”), 8 (“100”), 16 (“101”), 32 (“110”), or 64 (“111”)

entries from the bottom of the queue. The usable range for the Nearly

Empty Watermark selection is limited to a value less than the buffer

size.

UR/W

25:2

4

Buffer Size

These bits are used to configure the queue buffer size. The buffer size

can be configured for 16 (“00”), 32 (“01”), 64 (“10”) or 128 (“11”)

words

UR/W

23:2

2

Entry Size

These bits are used to configure the queue entry size of the queue.

The entry size can be set at 1 (“00”) or 2 (“01”) or 4 (“10”) words. An

input of “11” results in the entry size being set at 1.

UR/W

21:1

4

Base Address

This field is used to configure the starting base address of the queue.

The read and write pointer are offset addresses from the base

address. This base address is a SRAM 16 word address. Base

addresses, 00 to 03, are reserved for the Queue Configuration Words.

The most significant bit of the base address will be reserved for growth

to a 16 KB SRAM, thus providing 8 KB of additional queue buffer

space.

UR/W

13:7 Read Pointer

This is a pointer to the next entry to be read from the queue. The

pointer is the AQM’s internal SRAM word address. In general, this

pointer should initialized to zero, and not be written except for

diagnostic or test purposes.

UR/W

6:0 Write Pointer

This is a pointer to the next entry to be written to the queue. The

pointer is the AQM’s internal SRAM word address. In general, this

pointer should initialized to zero, and not be written except for

diagnostic or test purposes.

UR/W