Intel

®

IXP42X product line and IXC1100 control plane processors—Ethernet MAC A

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

434 Order Number: 252480-006US

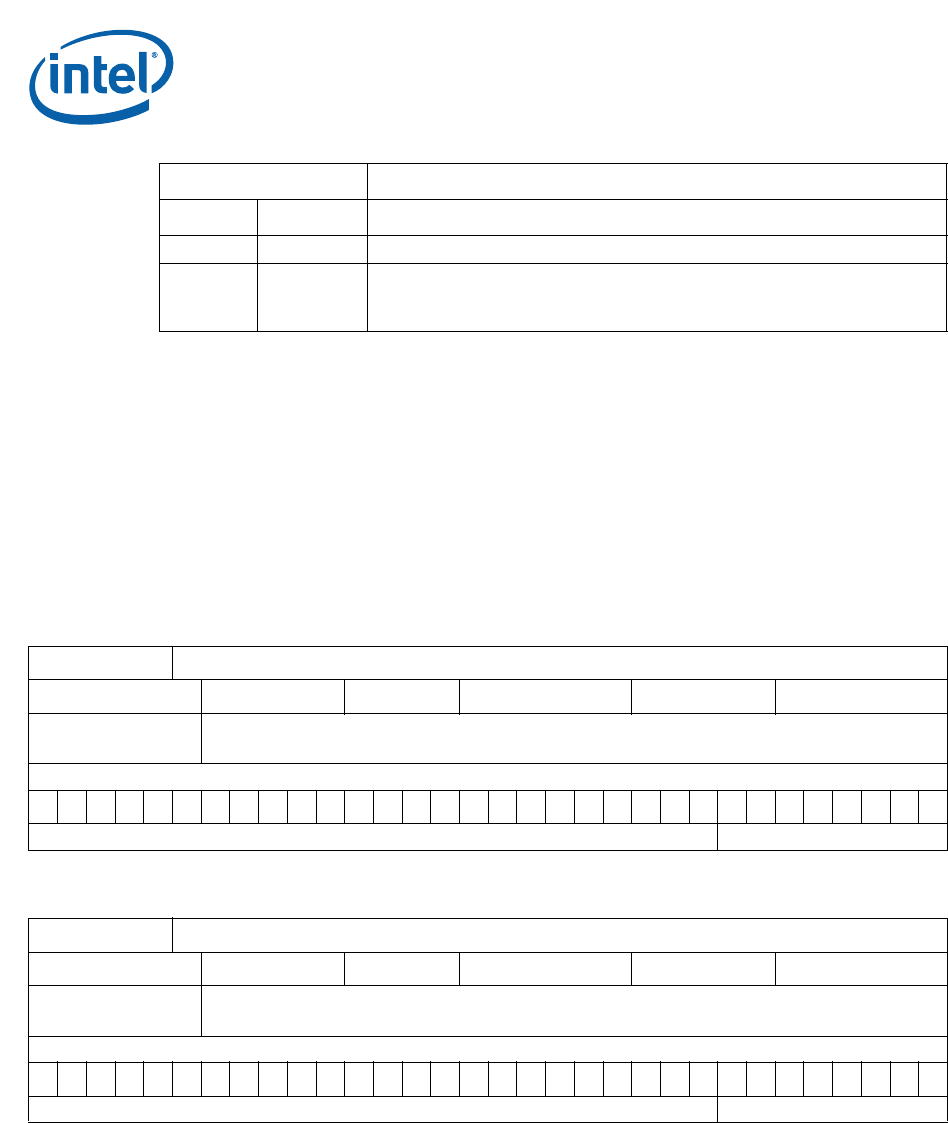

15.2.14 MDIO Commands Registers

Four registers make up the 32-bit MDIO Command that services both MII interfaces:

• MDIO Command[31:24] — MDIO Command 4

• MDIO Command[23:16] — MDIO Command 3

• MDIO Command[15:8] — MDIO Command 2

• MDIO Command[7:0] — MDIO Command 1

The detailed bit descriptions follow the four commands’ bit maps.

15.2.15 MDIO Command 1

15.2.16 MDIO Command 2

Register slottime

Bits Name Description

31:8 (Reserved)

7:0 Slot Time

Slot time for back-off algorithm

Expressed in number of tx_clk cycles.

128 in MII mode.

Register Name: mdiocmd1

Hex Offset Address: 0xC8009080 Reset Hex Value: 0x00000000

Register

Description:

MDIO Command 1 (8 Bits of 32-Bit Register).

Access: Read/Write.

70

MDIO Command [7:0]

Register Name: mdiocmd2

Hex Offset Address: 0x C8009084 Reset Hex Value: 0x00000000

Register

Description:

MDIO Command Register

Access: Read/Write.

31 87 0

(Reserved) MDIO_COMMAND [15:8]