Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 523

Universal Serial Bus (USB) v1.1 Device Controller—Intel

®

IXP42X product line and IXC1100

control plane processors

18.5.22.2 Isochronous Packet Error Endpoint 4 (IPE4)

The isochronous packet error for Endpoint 4 is set if Endpoint 4 is loaded with a data

packet that is corrupted. This status bit is used in the interrupt generation of endpoint 4.

To maintain synchronization, the software must monitor this bit when it services an

SOF interrupt and reads the frame number. This bit is not set if the token packet is

corrupted or if the sync or PID fields of the data packet are corrupted.

18.5.22.3 Isochronous Packet Error Endpoint 9 (IPE9)

The isochronous packet error for Endpoint 9 is set if Endpoint 9 is loaded with a data

packet that is corrupted. This status bit is used in the interrupt generation of endpoint 9.

To maintain synchronization, software must monitor this bit when it services the SOF

interrupt and reads the frame number. This bit is not set if the token packet is

corrupted or if the sync or PID fields of the data packet are corrupted.

18.5.22.4 Isochronous Packet Error Endpoint 14 (IPE14)

The isochronous packet error for Endpoint 14 is set if Endpoint 14 is loaded with a data

packet that is corrupted. This status bit is used in the interrupt generation of endpoint 14.

To maintain synchronization, software must monitor this bit when it services the SOF

interrupt and reads the frame number. This bit is not set if the token packet is

corrupted or if the sync or PID fields of the data packet are corrupted.

18.5.22.5 Start of Frame Interrupt Mask (SIM)

The UFNHR[SIM] bit is used to mask or enable the SOF interrupt request. When

UFNHR[SIM]=1, the interrupt is masked and the SIR bit is not allowed to be set. When

UFNHR[SIM]=0, the interrupt is enabled and when an interruptible condition occurs in

the receiver, the UFNHR[SIR] bit is set.

Setting UFNHR[SIM] to a 1 does not affect the current state of UFNHR[SIR]. It only

blocks future zero to one transitions of UFNHR[SIR].

18.5.22.6 Start of Frame Interrupt Request (SIR)

The interrupt request bit is set if the UFNHR[SIM] bit is cleared and an SOF packet is

received.

The UFNHR[SIR] bit is cleared by writing a 1 to it.

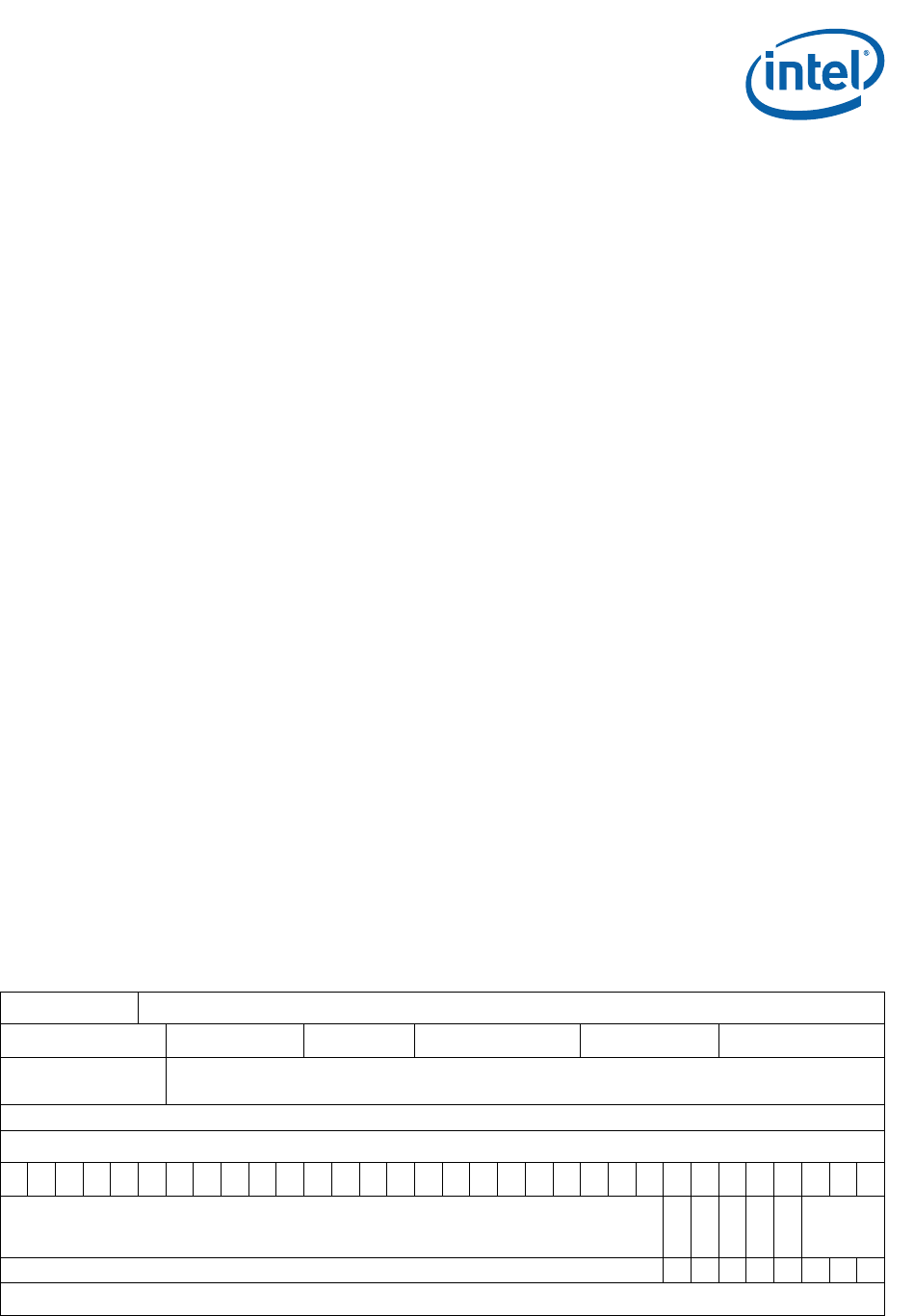

Register Name: UFNHR

Hex Offset Address: 0 x C800B060 Reset Hex Value: 0x00000040

Register

Description:

Universal Serial Bus Device Frame Number High Register

Access: Read-Only

Bits

31 876543210

(Reserved)

SIR

SIM

IPE14

IPE9

IPE4

3-Bit

Frame

Number

MSB

X 01000000

Resets (Above)