Intel

®

IXP42X product line and IXC1100 control plane processors—Interrupt Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

402 Order Number: 252480-006US

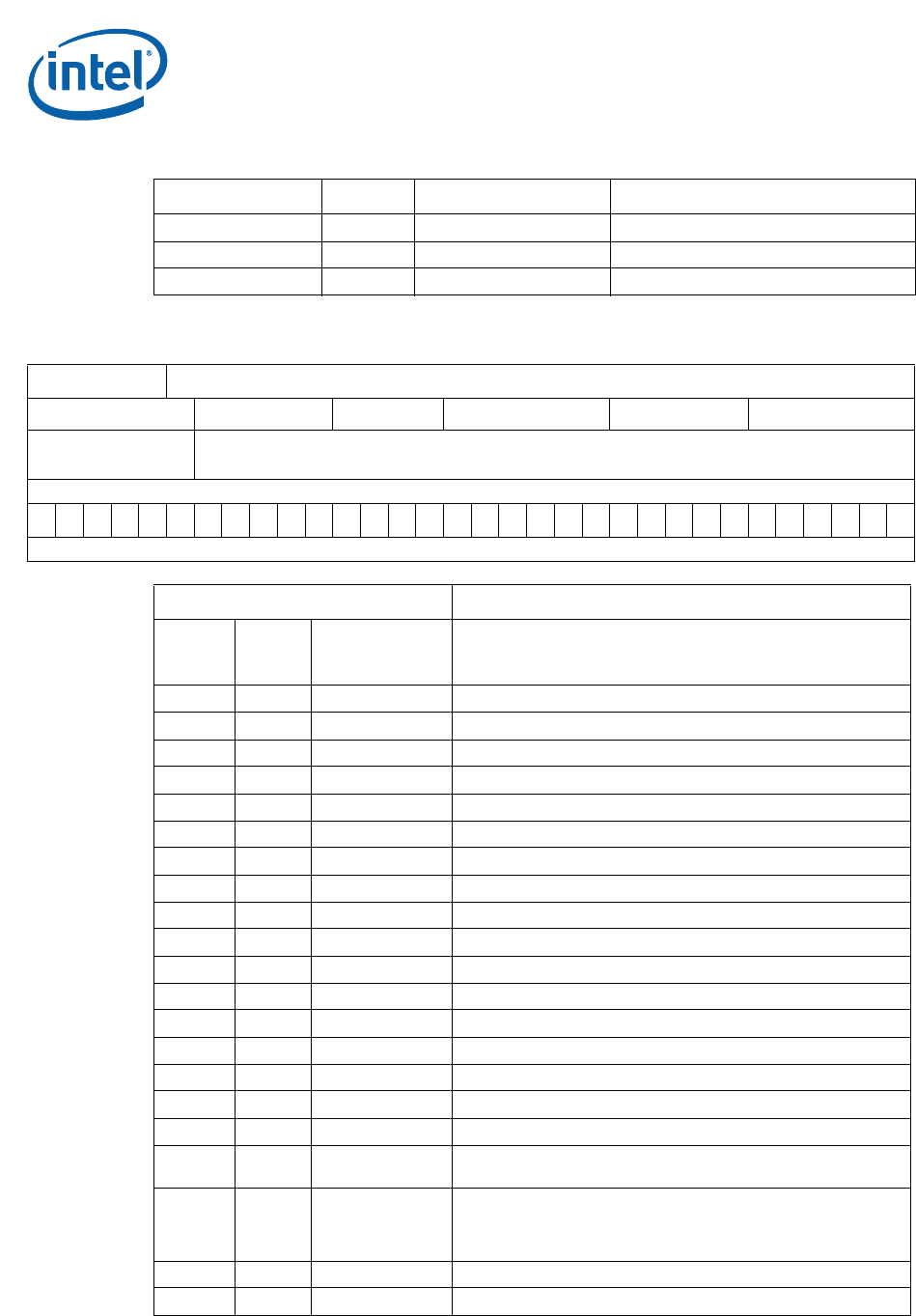

13.5.1 Interrupt Status Register

0xC8003014 R/W INTR_PRTY Interrupt Priority Register

0xC8003018 R INTR_IRQ_ENC_ST IRQ Highest Priority Register

0xC800301C R INTR_FIQ_ENC_ST FIQ Highest Priority Register

Register Name: INTR_ST

Hex Offset Address: 0xC800 3000 Reset Hex Value: 0x00000000

Register

Description:

This register indicates the state of each incoming interrupt.

Access: Read.

31 0

Incoming Interrupt Status

Register

INTR_ST (Sheet 1 of 2)

Interrup

t Bit

Default

Priority

1

Source Description

Int0 0 WAN/Voice NPE Debug/Execution/MBox

Int1 1 Ethernet NPE A Debug/Execution/MBox

Int2 2 Ethernet NPE B Debug/Execution/MBox

Int3 3 Queue Manager Queue[1-32]

Int4 4 Queue Manager Queue[33-64]

Int5 5 Timers General-Purpose Timer 0

Int6 6 GPIO GPIO[0]

Int7 7 GPIO GPIO[1]

Int8 8 PCI PCI Interrupt

Int9 9 PCI PCI DMA Channel 1

Int10 10 PCI PCI DMA Channel 2

Int11 11 Timers General-Purpose Timer 1

Int12 12 USB USB

Int13 13 Console UART Console UART

Int14 14 Timers Timestamp Timer

Int15 15 High-Speed UART High-Speed UART

Int16 16 Timers Watchdog Timer

Int17 17

Performance

Monitoring Unit

Performance Monitoring Unit counter rollover

Int18 18

Intel XScale

®

Processor

Performance

Monitoring Unit

Intel XScale processor PMU counter rollover

Int19 19 GPIO GPIO[2]

Int20 20 GPIO GPIO[3]

Table 149. Interrupt Controller Registers

Address R/W Name Description