Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 361

Universal Asynchronous Receiver Transceiver (UART)—Intel

®

IXP42X product line and IXC1100

control plane processors

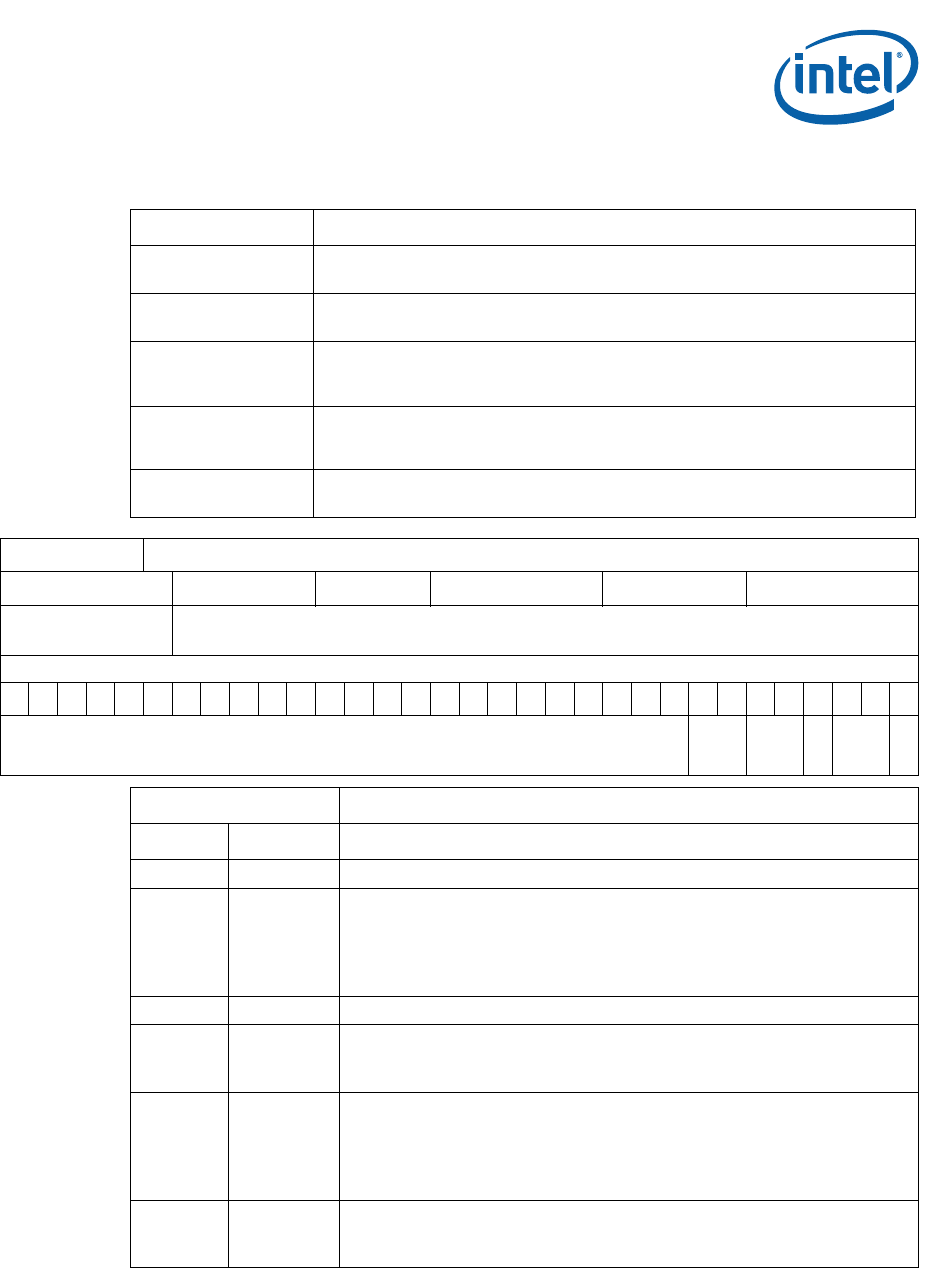

Table 137. Priority Levels of Interrupt Identification Register

Priority Level Interrupt origin

1

(Highest)

Receiver Line Status:

One or more error bits were set.

2

Received Data is Available:

In FIFO mode, trigger level was reached. In non-FIFO mode, RBR has data.

2

Receiver Time Out Occurred:

It happens in FIFO mode only, when there is data in the receive FIFO but no activity

for a time period.

3

Transmitter Requests Data:

In FIFO mode, the transmit FIFO is half or more than half empty. In non-FIFO

mode, THR is read already.

4

(Lowest)

Modem Status:

One or more of the modem input signals has changed state.

Register Name: IIR

Hex Offset Address: 0xC800 1008 Reset Hex Value: 0x00000001

Register

Description:

Interrupt Identification Register

Access: Read Only.

31 876543210

(Reserved)

FIFOES

(Rsvd)

TOD

IID

IP_N

Register IIR

Bits Name Description

31:8 (Reserved)

7:6 FIFOES

FIFO Mode Enable Status:

00 = Non-FIFO mode is selected

01 = (Reserved)

10 = (Reserved)

11 = FIFO mode is selected (TRFIFOE = 1)

5:4 (Reserved)

3TOD

Time Out Detected:

0 = No time out interrupt is pending

1 = Time out interrupt is pending. (FIFO mode only)

2:1 IID

Interrupt Source Encoded:

00 = Modem Status (CTS, DSR, RI, DCD modem signals changed state)

01 = Transmit FIFO requests data

10 = Received Data Available

11 = Receive error (Overrun, parity, framing, break, FIFO error)

0IP_N

Interrupt Pending:

0 = Interrupt is pending. (Active low)

1 = No interrupt is pending