Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 323

Expansion Bus Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

These configuration bits are made available to the system as outputs from the

Expansion Bus Controller block. With the exception of bits 23, 22 and 21, which are

read only, all other bits may be written and read from the South AHB.

The chip-level memory map used is determined by the state of bit 31. At system reset

this bit is a ‘1’ and the memory map places the Expansion Bus at address 0x00000000

through 0x0FFFFFFF. This allows boot code stored in flash to be retrieved and executed

as required.

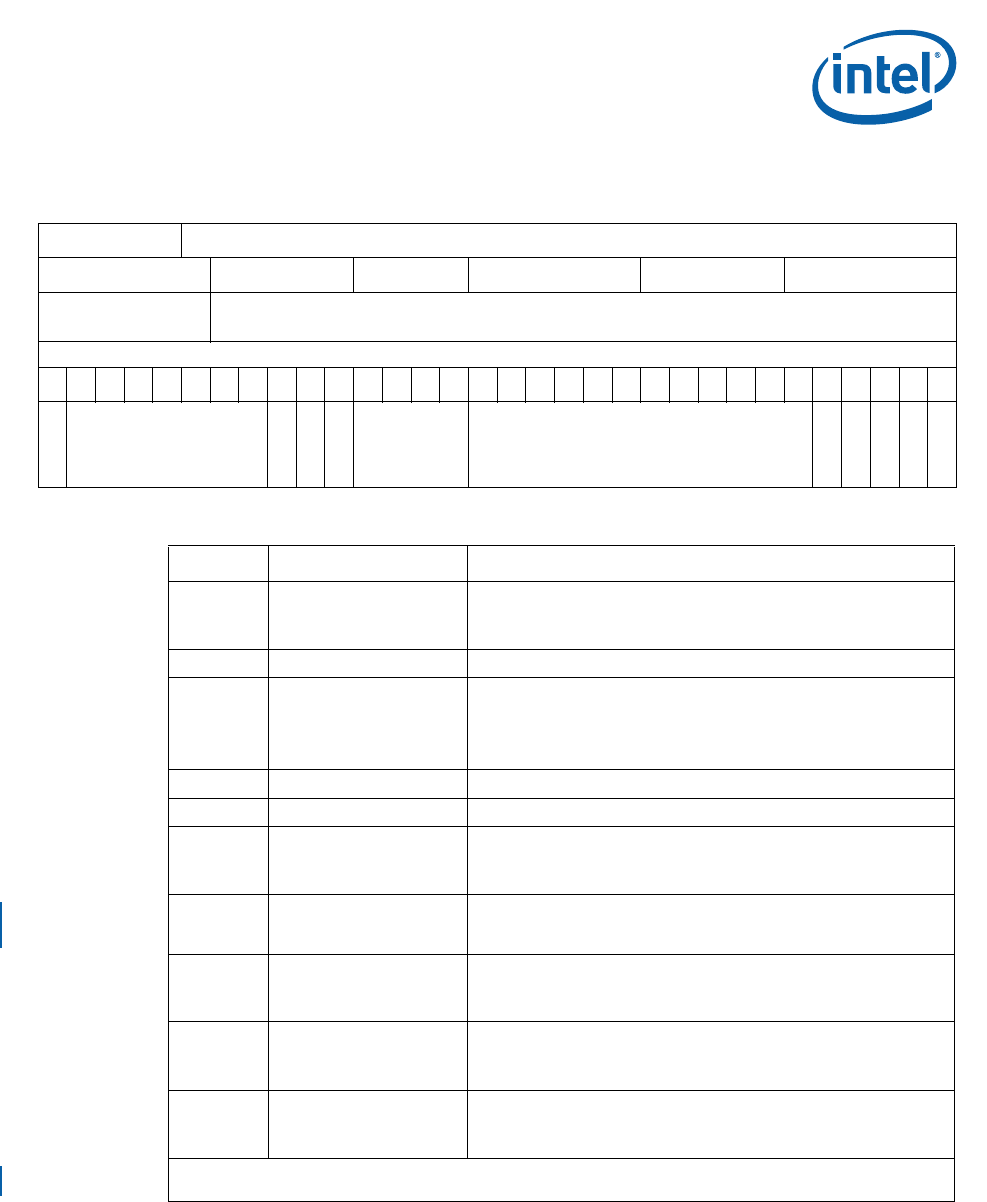

Register Name: EXP_CNFG0

Hex Offset Address: 0XC4000020 Reset Hex Value: 0x8XXXXXXX

Register

Description:

Configuration Register #0

Access: Read/Write.

3130 2423222120 1716 543210

MEM_MAP

(Reserved)

CLK bit 2

CLK Bit 1

CLK Bit 0

User-

configurable

(Reserved)

PCI_ CLK

RES

PCI_ARB

PCI_ HOST

8/16

Table 124. Configuration Register 0 Description

Bit Name Description

31 MEM_MAP

Location of EXPBus in memory map space:

0 = Located at “50000000” (normal mode)

1 = Located at “00000000” (boot mode)

30:24 (Reserved)

23:21

Intel XScale processor

Clock Set[2:0]

Allow a slower Intel XScale processor clock speed to override

device fuse settings. However cannot be used to over clock core

speed. Refer to Section 125, “Intel XScale® Processor Speed

Expansion Bus Configuration Strappings” on page 324 for

additional details.

20:17 User-configurable User-configurable. See Section 8.9.9.1 for additional comments.

16:5 (Reserved)

4PCI_CLK

Sets the clock speed of the PCI Interface

0 = 33 MHz

1 = 66 MHz

3

(Reserved). EX_ADDR[3] must not be pulled down during address

strapping. This bit must be written to ‘1’ if performing a write to

this register.

2PCI_ARB

Enables the PCI Controller Arbiter

0 = PCI arbiter disabled

1 = PCI arbiter enabled

1PCI_HOST

Configures the PCI Controller as PCI Bus Host

0 = PCI as non-host

1 = PCI as host

08/16 FLASH

Specifies the data bus width of the FLASH memory device

0 = 16-bit data bus

1 = 8-bit data bus

Note: The bits that are (Reserved) should remain reserved because they may be assigned to future

steppings of the IXP42X product line and IXC1100 control plane processors

.