Intel

®

IXP42X product line and IXC1100 control plane processors—Universal Serial Bus (USB)

v1.1 Device Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

530 Order Number: 252480-006US

Since it is double-buffered, up to two packets of data may be ready. Via direct read

from the Intel XScale

®

processor, the data can be removed from the UDC. If one

packet is being removed and the packet behind it has already been received, the UDC

will issue a NAK to the host the next time it sends an OUT packet to endpoint 2.

This NAK condition will remain in place until a full packet space is available in the UDC

at Endpoint 2.

18.5.33 UDC Data Register 3 (UDDR3)

Endpoint 3 is a double-buffered isochronous IN endpoint that is 256 bytes deep. Data

can be loaded via direct Intel XScale

®

processor writes.

Because it-is double-buffered, up to two packets of data may be loaded for

transmission.

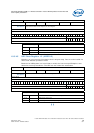

Register Name: UDDR2

Hex Offset Address: 0 x C800B180 Reset Hex Value: 0x00000000

Register

Description:

Universal Serial Bus Device Endpoint 2 Data Register

Access: Read

Bits

31 87 0

(Reserved) (8-Bit Data)

X 00000000

Resets (Above)

Register

UDDR2

Bits Name Description

31:8 Reserved for future use.

7:0 DATA Top of endpoint data currently being read.

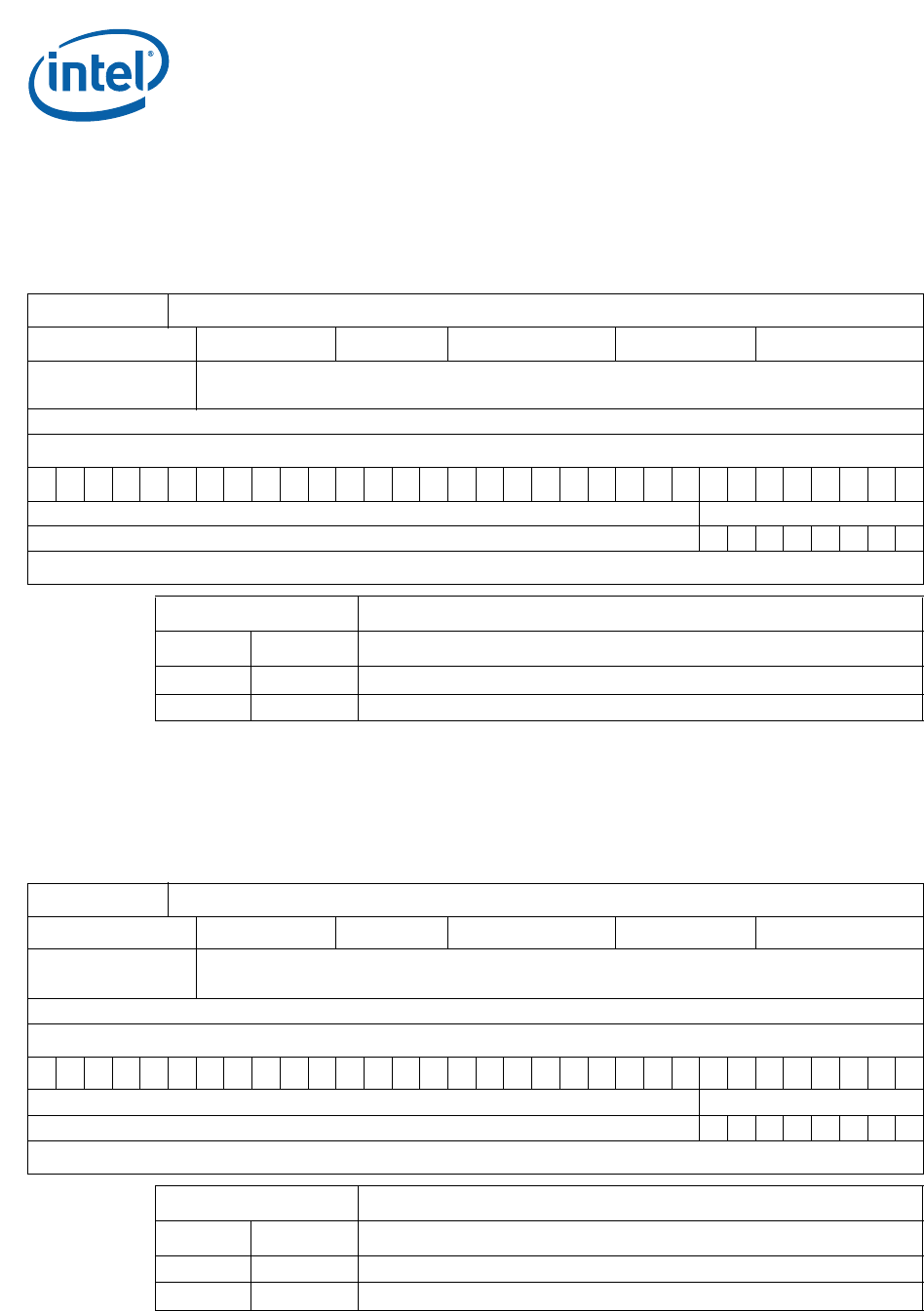

Register Name: UDDR3

Hex Offset Address: 0 x C800B200 Reset Hex Value: 0x00000000

Register

Description:

Universal Serial Bus Device Endpoint 3 Data Register

Access: Write

Bits

31 16 15 8 7 0

(Reserved) (8-Bit Data)

X 00000000

Resets (Above)

Register

UDDR3

Bits Name Description

31:8 Reserved for future use.

7:0 DATA Top of endpoint data currently being loaded.