Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 279

SDRAM Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

After decoding is complete, the SDRAM Controller completes the read or write

transaction to the SDRAM.

Byte and half-word transfers are implemented by controlling the DQM pins of the

SDRAM. The SDRAM Controller performs byte lane steering for write operations to the

SDRAM. Read operations performed by the SDRAM Controller to the SDRAM do not

support byte-lane steering. Read operations performed by the SDRAM Controller to the

SDRAM must be 32-bits. If sub-word accesses are requested a full 32-bits will be

returned.

7.1 SDRAM Memory Space

The SDRAM memory space is defined with the base address beginning at hexadecimal

0x00000000 and ending at hexadecimal 0x3FFFFFFF.

The SDRAM memory space overlaps the expansion bus memory space during the boot

sequence. Once the boot sequence has started, a configuration register — located in

the expansion bus configuration space — must be written to remove the expansion bus

mapping from the SDRAM space. Therefore enabling the SDRAM memory space to start

in hexadecimal location 0x000000000.

The mapping of the SDRAM and Expansion Bus is described in detail in Section 8.9.9,

“Configuration Register 0” on page 322.

During a read or write access, only one chip-select pin — SDR_CS_N (SDRAM Chip

Select) — will be active at a time.

7.2 Initializing the SDRAM Controller

In order to use the SDRAM interface, the device must be configured properly. There are

three configuration registers used to initialize the SDRAM Controller. Before using the

SDRAM Controller, the SDRAM Configuration (SDR_CONFIG) Register must be

initialized.

The SDRAM Configuration (SDR_CONFIG) Register will provide the CAS to data delay

parameter and the external Memory Configuration. Bit 3 of the SDRAM Configuration

(SDR_CONFIG) Register is used to specify the CAS to data delay. After reset, the CAS-

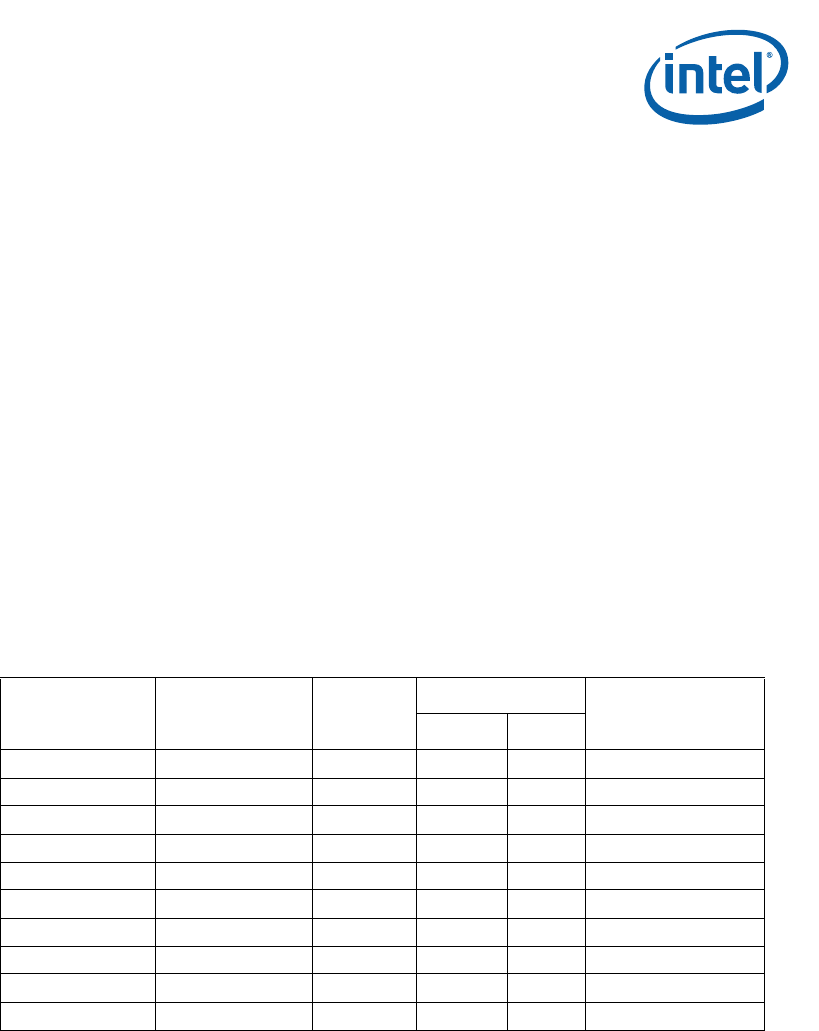

Table 106. Memory Space

SDRAM Tech. SDRAM Type # Chips

Address Size

Total Mem. Size

Row Column

64 Mbit 2 M x32 1 11 8 8 Mbyte

2 11 8 16 Mbyte

64 Mbit 4 M x16 2 12 8 16 Mbyte

4 12 8 32 Mbyte

128 Mbit 8 M x16 2 12 9 32 Mbyte

4 12 9 64 Mbyte

256 Mbit 16 M x16 2 13 9 64 Mbyte

4 13 9 128 Mbyte

512 Mbit 32 M x16 2 13 10 128 Mbyte

4 13 10 256 Mbyte