Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 357

Universal Asynchronous Receiver Transceiver (UART)—Intel

®

IXP42X product line and IXC1100

control plane processors

10.5 Console UART

The Console Universal Asynchronous Receiver-Transmitter (UART) behaves exactly like

the High-Speed UART. Speed will be programmable between 1,200 Baud to 231 KBaud.

10.5.1 Register Description

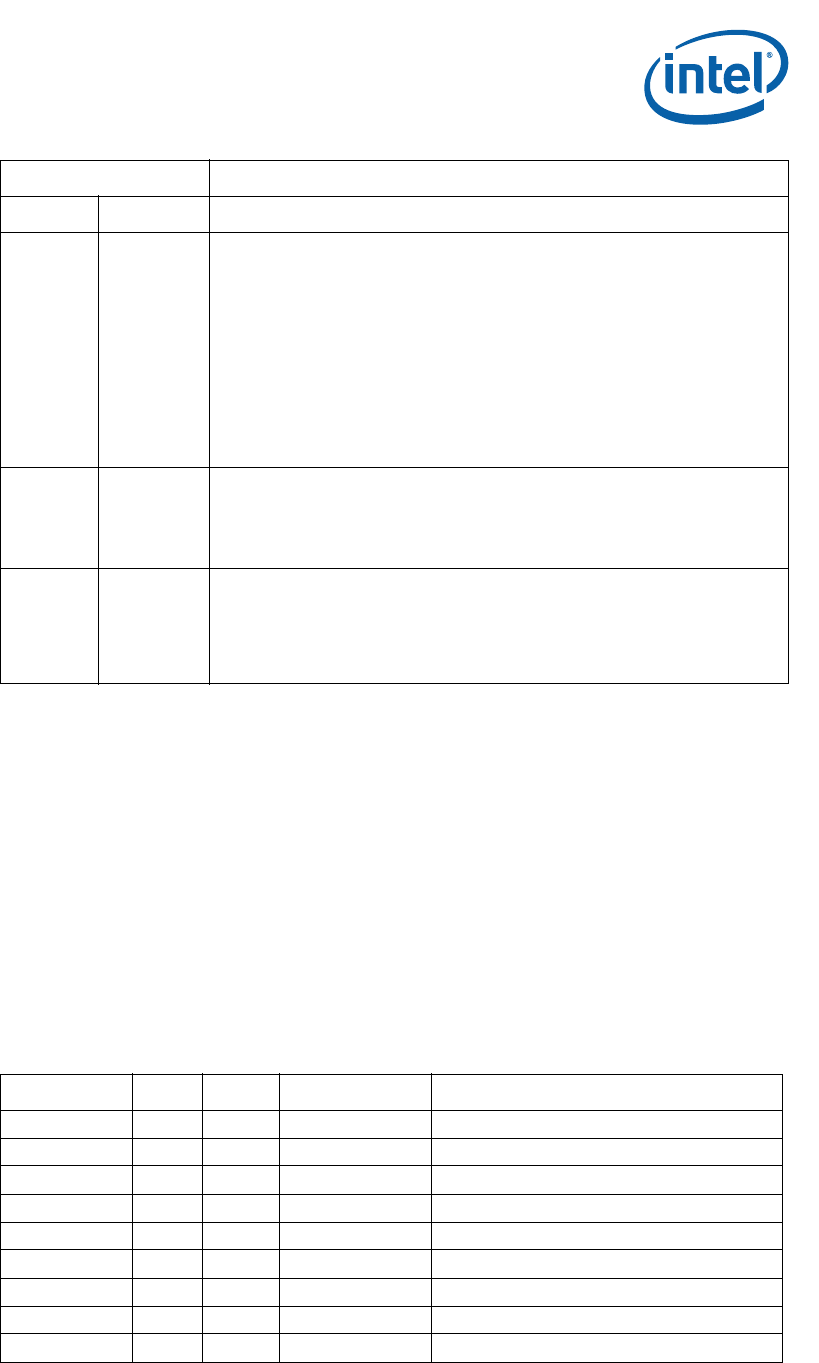

There are 13 registers to monitor and control the UART. The registers are all 32 bits in

size, but only lower 8 bits have valid data. The 13 UART registers share nine address

locations in the I/O address space.

Note that the state of the Divisor Latch Bit (DLAB) — the most-significant bit of the

Serial Line Control Register — affects the selection of certain of the UART registers. The

DLAB bit must be set high by the system software to access the Baud Rate Generator

Divisor Latches.

2XMODE

Transmit Pulse Width Select: When XMODE is set to 0, clocking of the IRDA

transmit and receive logic is done by the UART clock, which must be operating

in the 16X mode. When XMODE is set to a 1, the operation of the receive

decoder does not change. The transmit encoder, however, generates pulses

1.6 µs wide (which is three clock periods at frequency 1.8432 MHz) — instead of

the normal 3/16th of a bit time wide.

The shorter infrared pulse — generated with XMODE set to 1 — reduces the

power consumed by the LEDs. At 2,400 bps, the LED would normally be

activated for 78 µs for each 0 bit transmitted. With XMODE set, the LED would

be activated for only 1.6 µs.

This would reduce the power consumed by the LED by a factor of almost 48.

0 = Transmit pulse width is 3/16

th

of a bit time wide

1 = Transmit pulse with is 1.6us

1RCVEIR

Receiver SIR Enable: When the RCVEIR bit is set to logic 1, the IRDA decoder

processes the signal from the rxd pin. If RCVEIR is cleared, all clocking to the

IRDA decoder is blocked and the device’s rxd pin is fed directly to the UART.

0 = Receiver input is in normal UART mode

1 = Receiver input is in infrared mode

0XMITIR

Transmitter SIR Enable: When the XMITIR bit is set to logic 1, the IRDA

encoder processes the normal txd output from the UART before it is fed to the

device pin. If XMITIR is cleared, all clocking to the IRDA encoder is blocked and

the UART’s txd signal is connected directly to the device pin.

0 = Transmit output is in normal UART mode

1 = Transmit output is in infrared mode

Register

ISR (Sheet 2 of 2)

Bits Name Description

Table 136. Console UART Registers Overview

Address DLAB R/W Name Description

0xC8001000 0 R RBR Receive Buffer Register

0 W THR Transmit Holding Register

1 R/W DLL Divisor Latch Low Register

0x C8001004 0 R/W IER Interrupt Enable Register

1 R/W DLH Divisor Latch High Register

0x C8001008 0/1 R IIR Interrupt Identification Register

0/1 W FCR FIFO Control Register

0x C800100C 0/1 R/W LCR Line Control Register

0x C8001010 0/1 R/W MCR Modem Control Register