Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

62 Order Number: 252480-006US

The Intel XScale processor employs an eight entry write buffer, each entry containing

16 bytes. Stores to external memory are first placed in the write buffer and

subsequently taken out when the bus is available.

The write buffer supports the coalescing of multiple store requests to external memory.

An incoming store may coalesce with any of the eight entries.

The fill buffer holds the external memory request information for a data cache or mini-

data cache fill or non-cacheable read request. Up to four 32-byte read request

operations can be outstanding in the fill buffer before the Intel XScale processor needs

to stall.

The fill buffer has been augmented with a four entry pend buffer that captures data

memory requests to outstanding fill operations. Each entry in the pend buffer contains

enough data storage to hold one 32-bit word, specifically for store operations.

Cacheable load or store operations that hit an entry in the fill buffer get placed in the

pend buffer and are completed when the associated fill completes. Any entry in the

pend buffer can be pended against any of the entries in the fill buffer; multiple entries

in the pend buffer can be pended against a single entry in the fill buffer.

Pended operations complete in program order.

The following discussions refer to the data cache and mini-data cache as one cache

(data/mini-data) since their behavior is the same when accessed.

When the data/mini-data cache is enabled for an access, the data/mini-data cache

compares the address of the request against the addresses of data that it is currently

holding. If the line containing the address of the request is resident in the cache, the

access “hits” the cache. For a load operation the cache returns the requested data to

the destination register and for a store operation the data is stored into the cache. The

data associated with the store may also be written to external memory if write-through

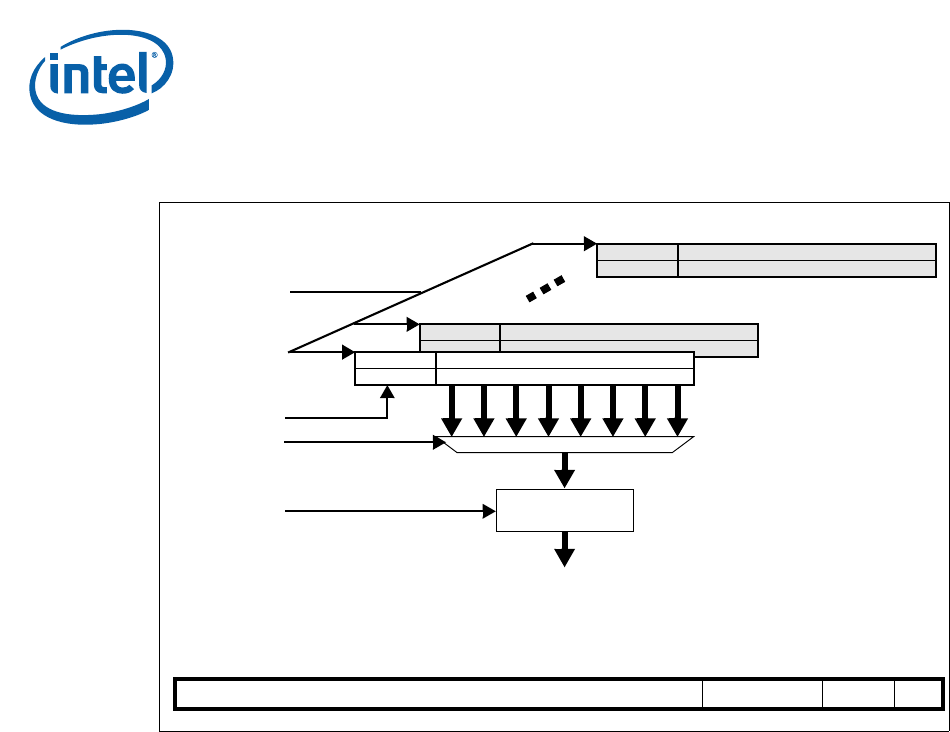

Figure 13. Mini-Data Cache Organization

way 0

way 1

32 bytes (cache line)

Set 1

way 0

way 1

32 bytes (cache line)

Set Index

Set 0

Tag

Data Word

(4 bytes to Destination Register)

Data Address (Virtual) — 2-Kbyte Cache

31 109 54 210

Tag Set Index Word Byte

Word Select

This example

shows Set 0

being selected by

the set index.

way 0

way 1

32 bytes (cache line)

Set 31

Byte Alignment

Sign Extension

Byte Select

Example: 2K byte cache