Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 107

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

The captured data is scanned out during the Shift_DR state.

Care must be taken while scanning in data. While polling TXRXCTRL[31], incorrectly

setting DBG_SR[35] or DBG_SR[1] may cause unpredictable behavior following an

Update_DR.

Update_DR parallel loads DBG_SR[35:1] into DBG_REG[34:0]. Whether the new data

gets written to the RX register or an overflow condition is detected depends on the

inputs to the RX write logic.

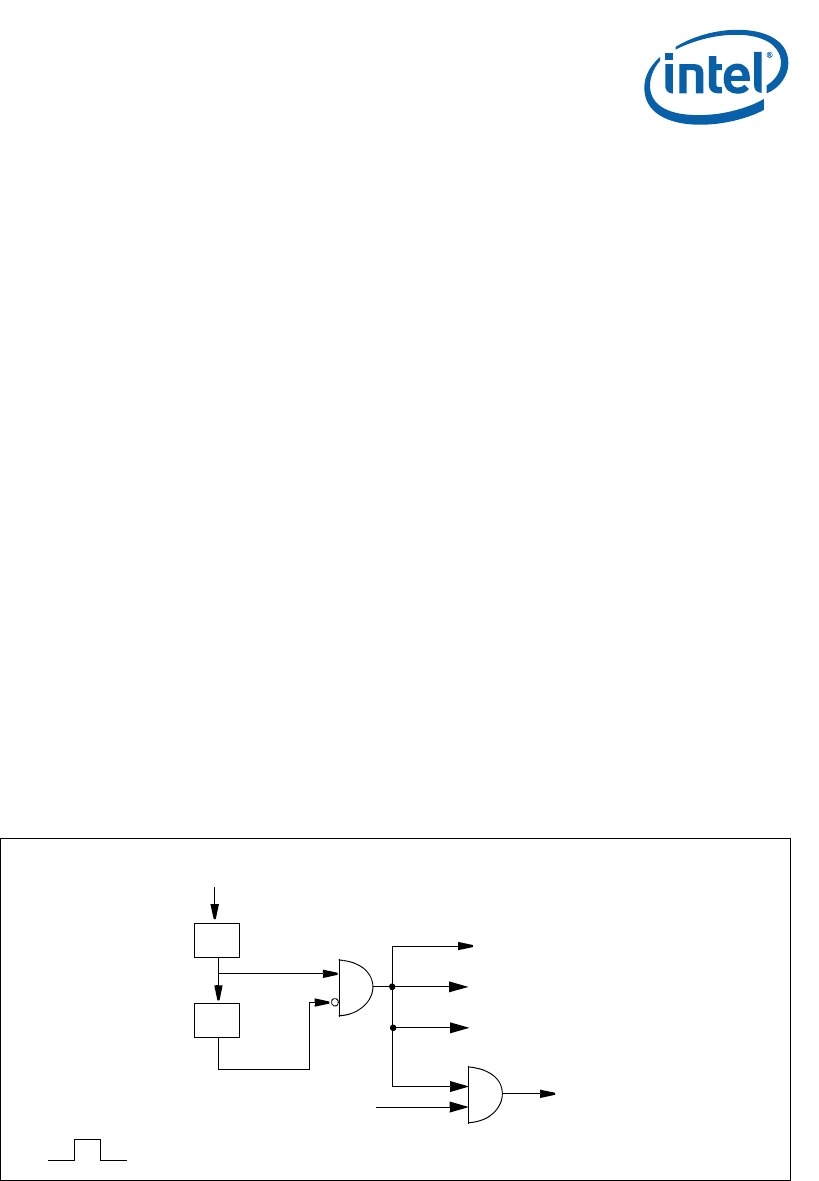

3.6.11.6.1 Rx Write Logic

The RX write logic (Figure 20) serves 4 functions:

• Enable the debugger write to RX - the logic ensures only new, valid data from the

debugger is written to RX. In particular, when the debugger polls TXRXCTRL[31] to

see whether the debug handler has read the previous data from RX. The JTAG state

machine must go through Update_DR, which should not modify RX.

• Clear DBG_REG[34] - mainly to support high-speed download. During high-speed

download, the debugger continuously scan in a data to send to the debug handler

and sets DBG_REG[34] to signal the data is valid. Since DBG_REG[34] is never

cleared by the debugger in this case, the ‘0’ to ‘1’ transition used to enable the

debugger write to RX would not occur.

• Set TXRXCTRL[31] - When the debugger writes new data to RX, the logic

automatically sets TXRXCTRL[31], signalling to the debug handler that the data is

valid.

• Set the overflow flag (TXRXCTRL[30] - During high-speed download, the debugger

does not poll to see if the handler has read the previous data. If the debug handler

stalls long enough, the debugger may overwrite the previous data before the

handler can read it. The logic sets the overflow flag when the previous data has not

been read yet, and the debugger has just written new data to RX.

3.6.11.6.2 DBGRX Data Register

The bits in the DBGRX data register (Figure 20) are used by the debugger to send data

to the processor. The data register also contains a bit to flush previously written data

and a high-speed download flag.

Figure 19. Rx Write Logic

Core CLK

DBG_REG[34]

TXRXCTRL[31]

Clear DBG_REG[34]

RX write enable

set TXRXCTRL[31]

set overflow flag

(TXRXCTRL[30])