Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 549

JTAG Interface—Intel

®

IXP42X product line and IXC1100 control plane processors

20.1.1 Test-Logic-Reset State

In Test-Logic-Reset State, test logic is disabled to allow normal operation of the chip.

Loading the IDCODE register disables test logic.

No matter what the state of the controller, it enters Test-Logic-Reset state when

JTG_TMS input is held high for at for five rising edges of JTG_TCK. The controller

remains in Test-Logic-Reset state while JTG_TMS is high. The TAP controller is also

forced to enter this state by enabling JTG_TRST_N.

If the controller exits the Test-Logic-Reset controller state as a result of an erroneous

low signal on the JTG_TMS line — at the time of a rising edge on JTG_TCK (for

example, a glitch due to external interference) — the state machine returns to the Test-

Logic-Reset state following three rising edges of JTG_TCK with the JTG_TMS line held at

logic 1.

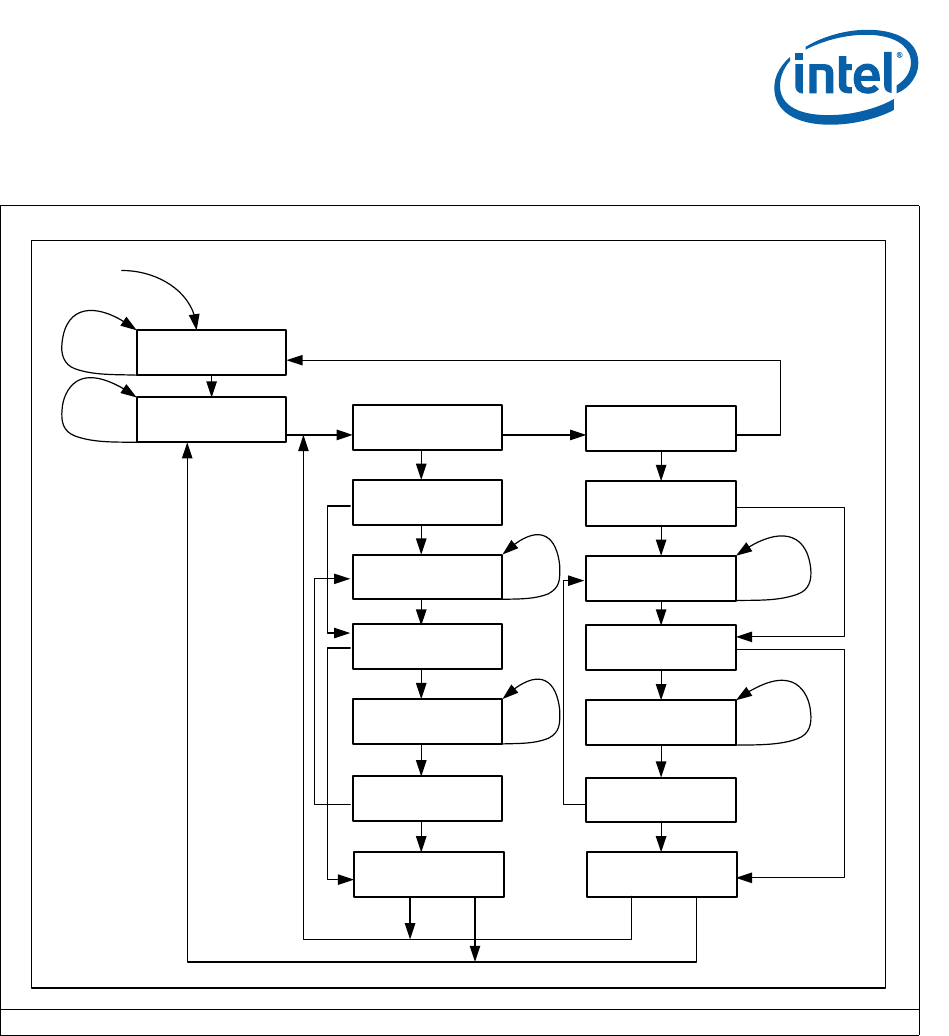

Figure 100. TAP Controller State Diagram

Note: Numbers associated with arrows indicate the value on the JTG_TMS signal.

TEST - LOGIC -

RESET

RUN - TEST /

IDLE

SELECT - DR -

SCAN

SELECT - IR -

SCAN

CAPTURE - DR

CAPTURE - IR

SHIFT - DR SHIFT - IR

EXIT - DR EXIT - IR

PAUSE - DR

PAUSE - IR

EXIT2 - DR EXIT2 - IR

UPDATE -DR

UPDATE -IR

1

0

0

1

1

0

0

1

0

1

1

0

0

0

1

1

1

0

0

0

0

0

1

1

1

1001

*Note: State transitions occur based on the

value of TMS on rising edge of TCK

1

0

1