Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

164 Order Number: 252480-006US

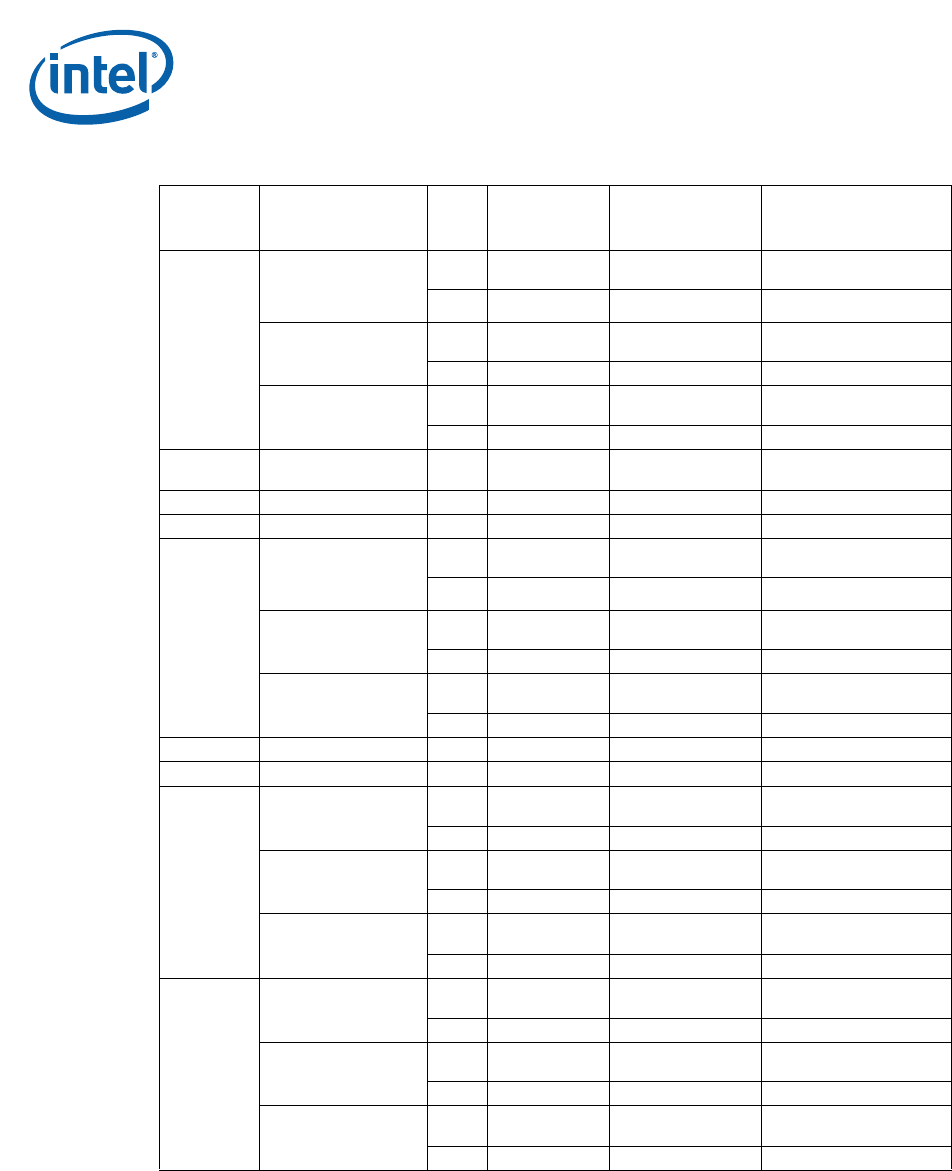

SMLAL

Rs[31:15] =

0x00000

or

Rs[31:15] = 0x1FFFF

02

RdLo = 2; RdHi =

3

2

13 3 3

Rs[31:27] = 0x00

or

Rs[31:27] = 0x1F

02

RdLo = 3; RdHi =

4

3

14 4 4

all others

02

RdLo = 4; RdHi =

5

4

15 5 5

SMLALxy N/A N/A 2

RdLo = 2; RdHi =

3

2

SMLAWy N/A N/A 1 3 2

SMLAxy N/A N/A 1 2 1

SMULL

Rs[31:15] =

0x00000

or

Rs[31:15] = 0x1FFFF

01

RdLo = 2; RdHi =

3

2

13 3 3

Rs[31:27] = 0x00

or

Rs[31:27] = 0x1F

01

RdLo = 3; RdHi =

4

3

14 4 4

all others

01

RdLo = 4; RdHi =

5

4

15 5 5

SMULWy N/A N/A 1 3 2

SMULxy N/A N/A 1 2 1

UMLAL

Rs[31:15] =

0x00000

02

RdLo = 2; RdHi =

3

2

13 3 3

Rs[31:27] = 0x00

02

RdLo = 3; RdHi =

4

3

14 4 4

all others

02

RdLo = 4; RdHi =

5

4

15 5 5

UMULL

Rs[31:15] =

0x00000

01

RdLo = 2; RdHi =

3

2

13 3 3

Rs[31:27] = 0x00

01

RdLo = 3; RdHi =

4

3

14 4 4

all others

01

RdLo = 4; RdHi =

5

4

15 5 5

Table 81. Multiply Instruction Timings (Sheet 2 of 2)

Mnemonic

Rs Value

(Early

Termination)

S-Bit

Valu

e

Minimum

Issue

Latency

Minimum Result

Latency

*

Minimum Resource

Latency (Throughput)

Note: If the next instruction needs to use the result of the multiply for a shift by immediate or as Rn in a

QDADD or QDSUB, one extra cycle of result latency is added to the number listed.