Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 381

Internal Bus Performance Monitoring Unit (IBPMU)—Intel

®

IXP42X product line and IXC1100

control plane processors

11.3.2 PMU Status Register (PSR)

The PSR allows access to the over flow flags from the PEC counters. These flags remain

set until cleared by writing a 1 to the bit.

11.3.3 Programmable Event Counters (PEC1)

There are seven programmable event counters (PEC1 – PEC7). These counters are 27

bits wide and are read-only.

The value in any register is incremented based on the current programmed ESR value.

If a new value is written to the ESR, all PEC counter registers are reset to 0. The

counters are halted when HALT mode is selected.

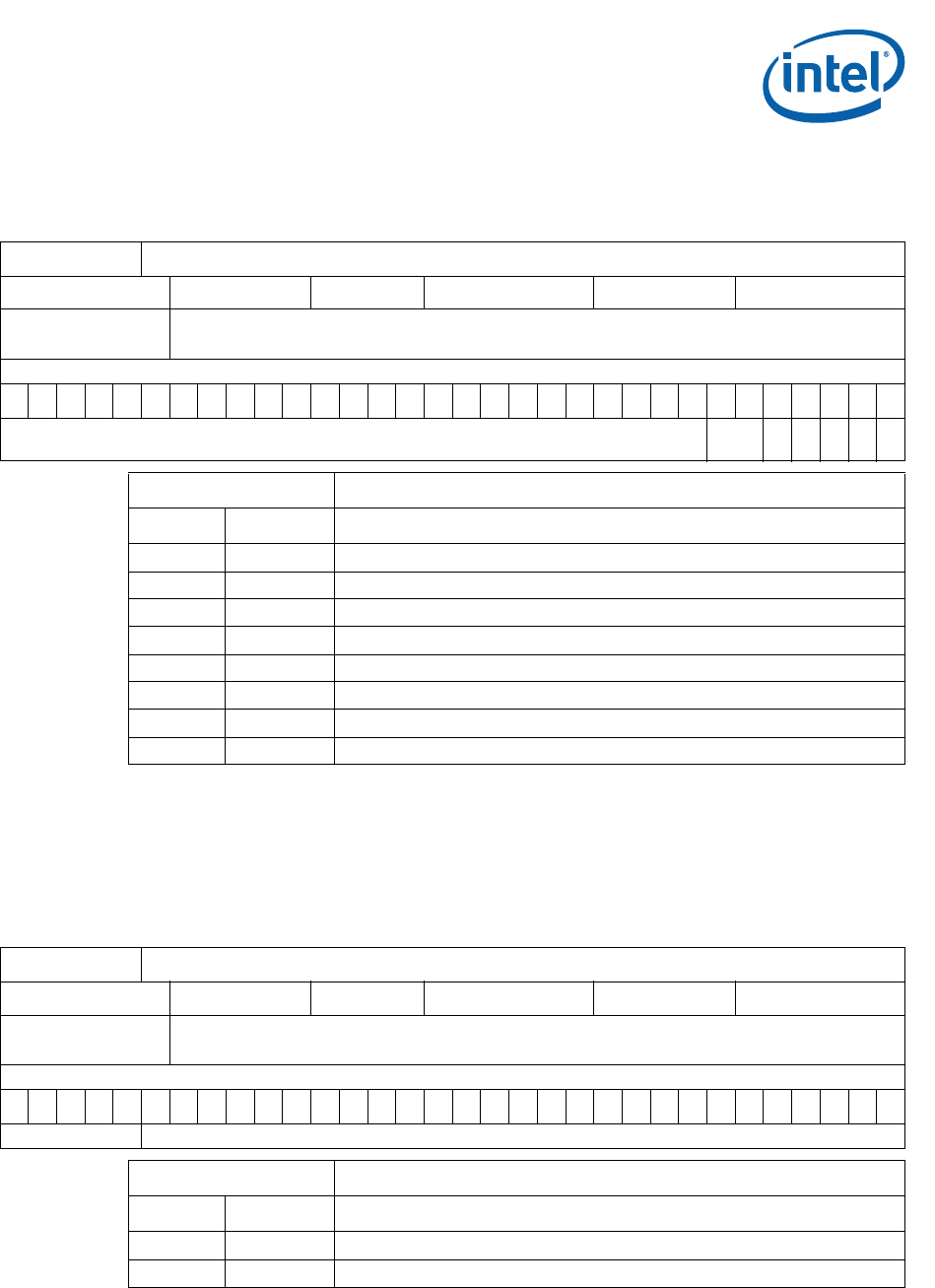

Register Name: PSR

Hex Offset Address: 0xC800 2004 Reset Hex Value: 0x00000000

Register

Description:

PMU Status Register

Access: Read, Clear on write.

31 76543210

(Reserved)

OFL7

OFL6

OFL5

OFL4

OFL3

OFL2

Register PSR

Bits Name Description

31:6 (Reserved). Always zero

6 OFL7 1 = PEC7 has overflowed

5 OFL6 1 = PEC6 has overflowed

4 OFL5 1 = PEC5 has overflowed

3 OFL4 1 = PEC4 has overflowed

2 OFL3 1 = PEC3 has overflowed

1 OFL2 1 = PEC2 has overflowed

0 OFL1 1 = PEC1 has overflowed

Register Name: PEC1

Hex Offset Address: 0xC800 2008 Reset Hex Value: 0x00000000

Register

Description:

Programmable Event Counter

Access: Read.

31 27 26 0

(Reserved) PEC1

Register

PEC1

Bits Name Description

31:27 (Reserved). Always 0

26:0 PEC1 This is a 27-bit, read-only counter register.