Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 363

Universal Asynchronous Receiver Transceiver (UART)—Intel

®

IXP42X product line and IXC1100

control plane processors

10.5.1.8 Line Control Register

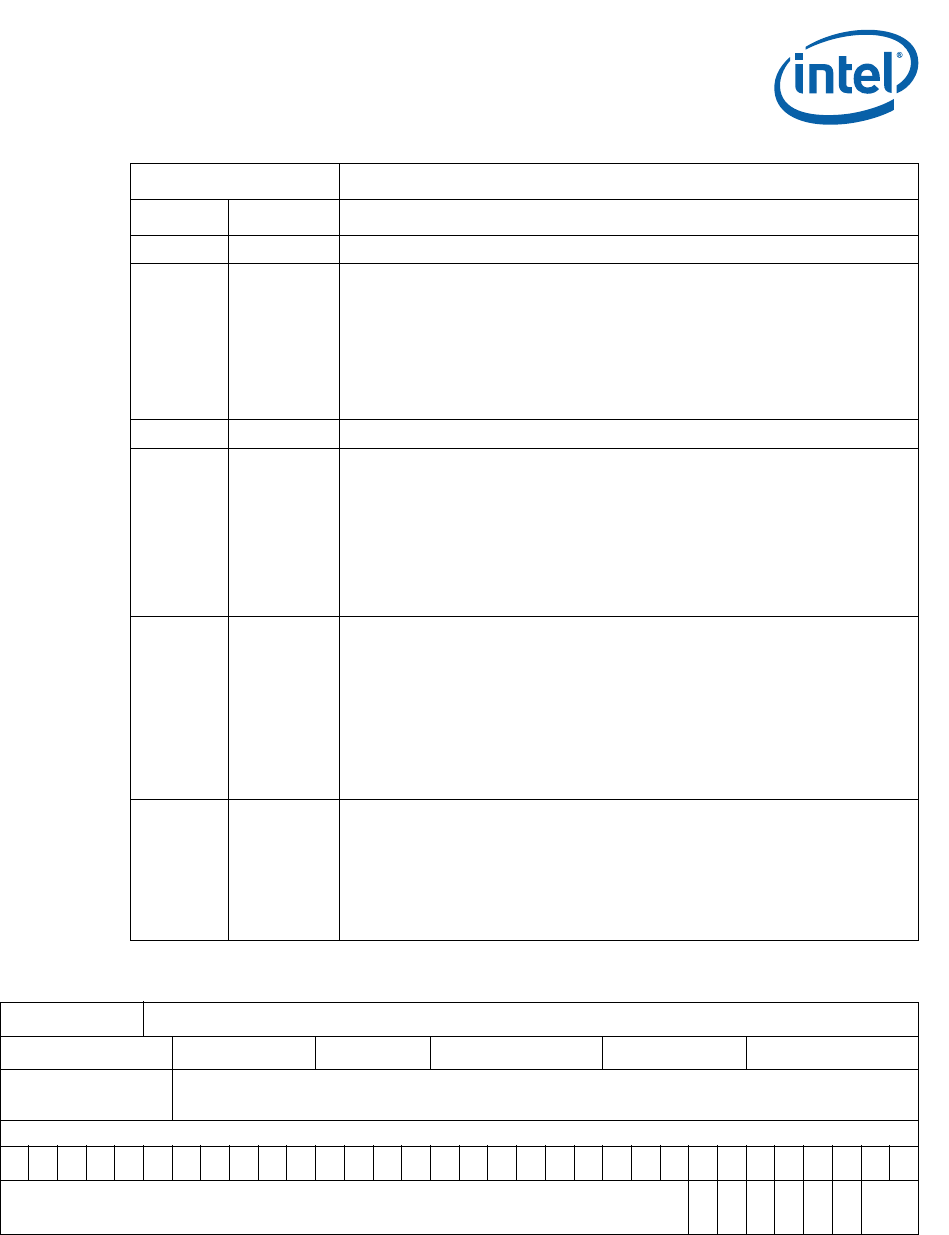

Register FCR

Bits Name Description

31:8 (Reserved)

7:6 ITL

Interrupt Trigger Level: When the number of entries in the receive FIFO

equals the interrupt trigger level programmed into this field and the Received

Data Available Interrupt is enabled (via IER), an interrupt is generated and

appropriate bits are set in the IIR.

00 = 1 byte or more in FIFO causes interrupt

01 = 8 bytes or more in FIFO causes interrupt

10 = 16 bytes or more in FIFO causes interrupt

11 = 32 bytes or more in FIFO causes interrupt

5:3 — Reserved

2RESETTF

Reset Transmitter FIFO: When RESETTF is logic 1, the transmitted FIFO

count logic is set to 0, effectively clearing all the entries in the transmit FIFO.

The TDRQ bit in LSR are set and IIR shows a transmitter requests data interrupt

if the TIE bit in the IER register is set. The transmitter shift register is not

cleared; it completes the current transmission.

After the FIFO is cleared, RESETTF is automatically reset to 0.

0 = Writing 0 has no effect

1 = The transmitter FIFO is cleared (FIFO counter set to 0). After clearing, bit is

automatically reset to 0

1RESETRF

Reset Receiver FIFO: When RESETRF is set to 1, the receive FIFO counter is

reset to 0, effectively clearing all the entries in the receive FIFO. The DR bit in

the LSR is reset to 0. All the error bits in the FIFO and the FIFOE bit in LSR are

cleared. Any error bits, OE, PE, FE or BI that had been set in LSR are still set.

The receiver shift register is not cleared. If IIR had been set to Received Data

Available, it is cleared. After the receive FIFO is cleared, RESETRF is

automatically reset to 0.

0 = Writing 0 has no effect

1 = The receiver FIFO is cleared (FIFO counter set to 0). After clearing, bit is

automatically reset to 0

0TRFIFOE

Transmit and Receive FIFO Enable: TRFIFOE enables/disables the

transmitter and receiver FIFO s.

When TRFIFOE = 1, both FIFOs are enabled (FIFO Mode). When TRFIFOE = 0,

the FIFO s are both disabled (non-FIFO Mode).

Writing a 0 to this bit clears all bytes in both FIFO s.

0 = FIFOs are disabled

1 = FIFOs are enabled

Register Name: LCR

Hex Offset Address: 0xC800 100C Reset Hex Value: 0x00000000

Register

Description:

Line Control Register

Access: Read-Write.

31 876543210

(Reserved)

DLAB

SB

STKYP

EPS

PEN

STB

WLS