Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 251

PCI Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

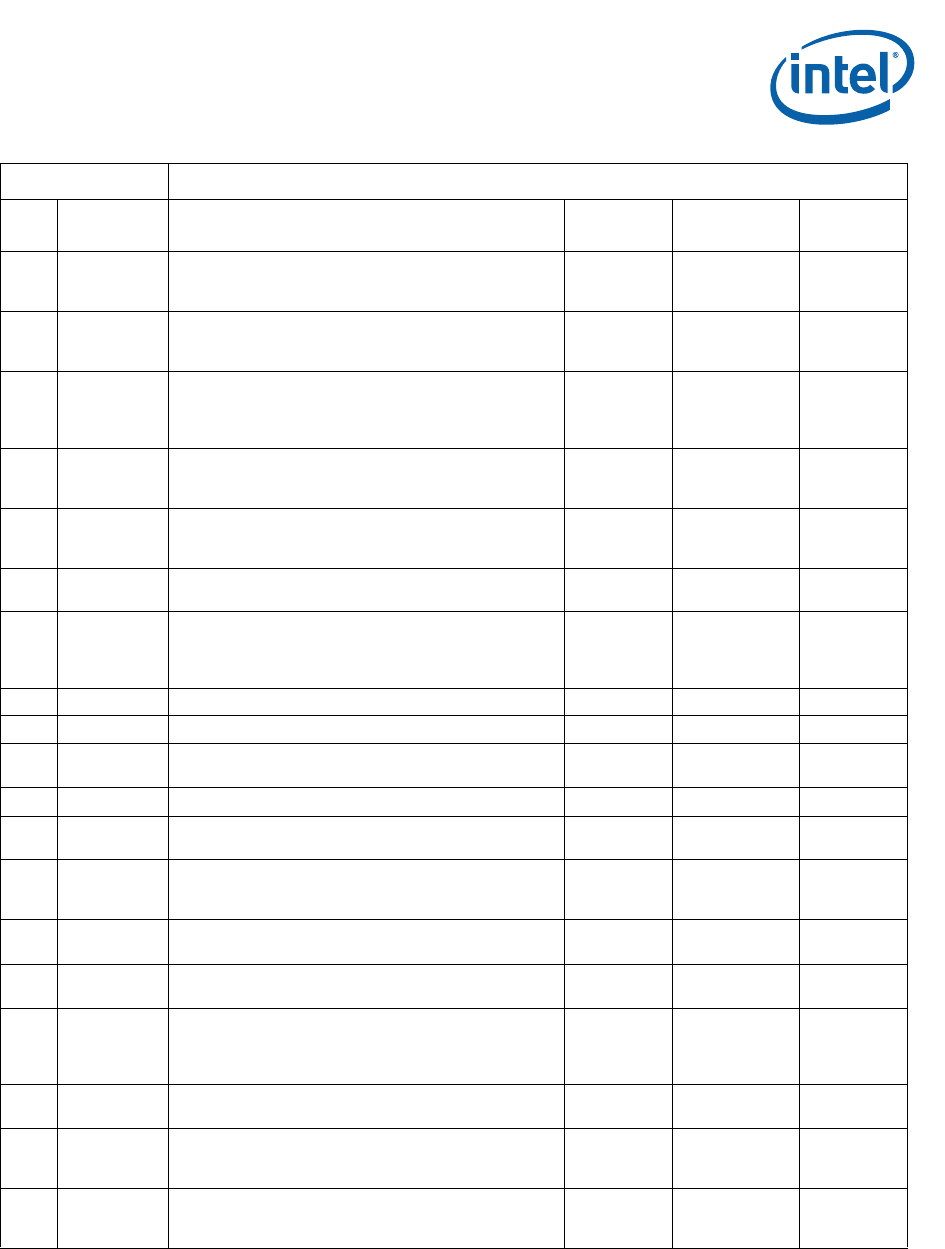

Register

PCI_SRCR (Sheet 1 of 2)

Bits Name Description

Reset

Value

PCI Access AHB Access

31 DPE

Detected Parity Error. Set when this device detects a

parity error on the bus even when parity handling is

disabled. Writing a 1 to this bit clears it.

0 RW1C RW1C

30 SSE

Signaled System Error. Set when this device

generates a System Error SERR#. Writing a 1 to this

bit clears it.

0 RW1C RW1C

29 RMA

Received Master Abort. Set by this device as a Master

when its transaction terminates due to a master abort

(except for special cycles). Writing a 1 to this bit

clears it.

0 RW1C RW1C

28 RTA

Received Target Abort. Set by this device as a Master

when its transaction is terminated due to a target

abort. Writing a 1 to this bit clears it.

0 RW1C RW1C

27 STA

Signaled Target Abort. Set by this device as a Target

when it terminates a transaction with a target abort.

Writing a 1 to this bit clears it.

0 RW1C RW1C

26:2

5

DEVSEL

Defines the DEVSEL speed for this device. Set to

medium.

01 RO RO

24 MDPE

Master Data Parity Error. Set by this device as a

Master if PER (bit 6) is set and this device either

asserted the PERR# signal or saw PERR# asserted for

one of its data phases.

0 RW1C RW1C

23 FBBC Fast Back-to-Back Capable. 1 RO RO

22 UDF User Definable Features supported. 0 = not supported 0 RO RO

21 66MHZ

66MHz Capable. Indicates if this device is capable of

66-MHz operation. 1 = 66MHz capable.

1RORW

20 CLI Capabilities List Indicator, Not supported 0 RO RO

19:1

0

-(Reserved) 00 RO RO

9 FBBE

Fast Back-to-Back Enable. When set to a 1 enables

the device to generate fast back-to-back cycles to

different targets as a Master.

0RWRW

8SER

System Error Enable. When set to a 1, enables the

SERR# output driver. 0 disables the driver.

0RWRW

7SC

Stepping Control. When set to a 1, enables address

stepping on the bus. This feature not supported.

0RORO

6PER

Parity Error Response. When set to a 1, enables

reporting of parity errors on PERR#. When set to 0,

parity errors not reported on PERR# but the DPE bit

(bit 31) is still set.

0RWRW

5PSE

Palette Snoop Enable. When set to a 1, enables VGA

palette snooping. This feature not supported.

0RORO

4MWIE

Memory Write and Invalidate Enable. When set to a

one, enables this device to generate the memory

write and invalidate command.

0RWRW

3SCE

Special Cycle Enable. When set, enables this device to

monitor for Special Cycles. This feature not

supported.

0RORO