Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

80 Order Number: 252480-006US

3.5.1.4 Register 3: Domain Access Control Register

3.5.1.5 Register 4: Reserved

Register 4 is reserved. Reading and writing this register yields unpredictable results.

3.5.1.6 Register 5: Fault Status Register

The Fault Status Register (FSR) indicates which fault has occurred, which could be

either a prefetch abort or a data abort. Bit 10 extends the encoding of the status field

for prefetch aborts and data aborts. The definition of the extended status field is found

in “Event Architecture” on page 154. Bit 9 indicates that a debug event occurred and

the exact source of the event is found in the debug control and status register (CP14,

register 10). When bit 9 is set, the domain and extended status field are undefined.

Upon entry into the prefetch abort or data abort handler, hardware will update this

register with the source of the exception. Software is not required to clear these fields.

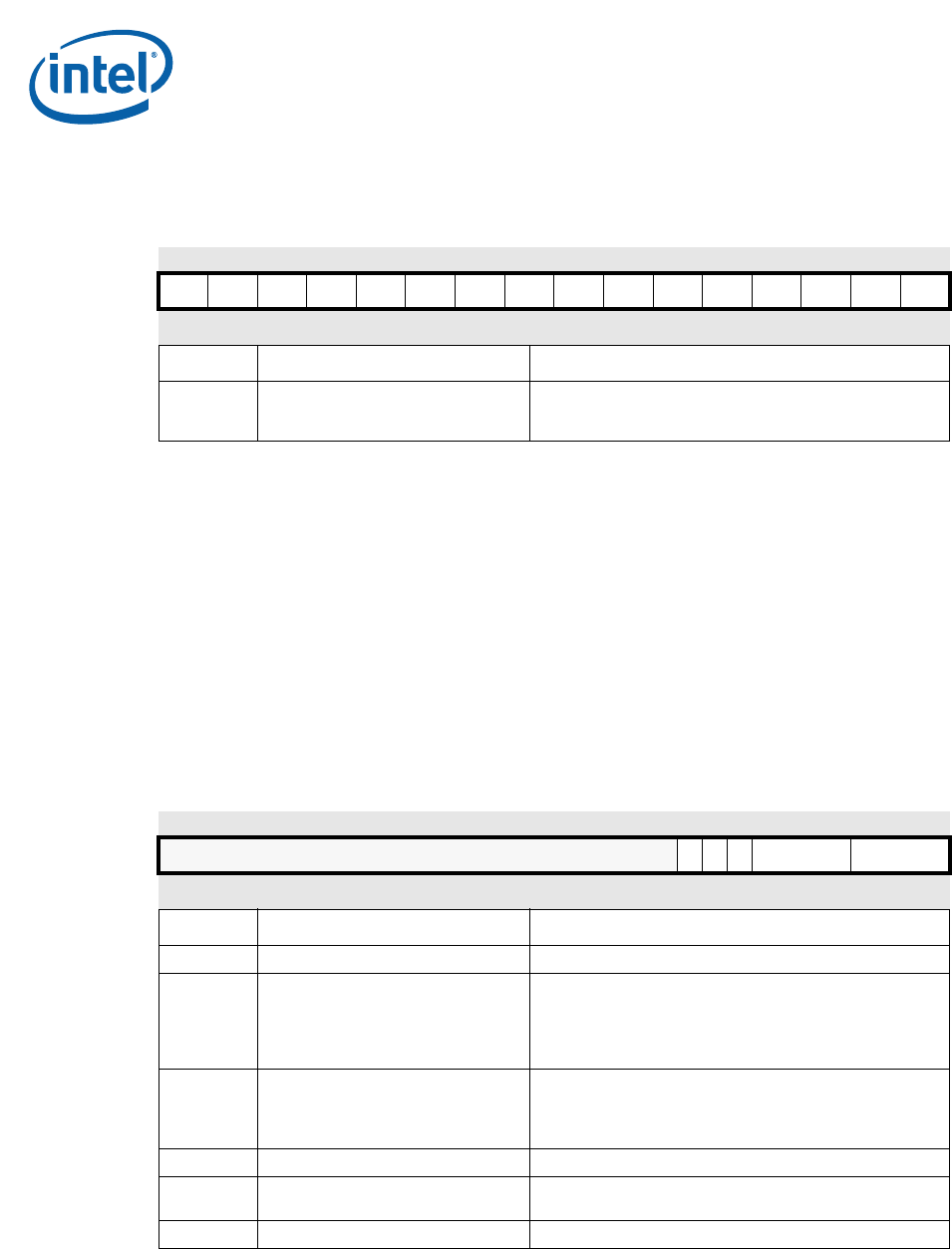

Table 15. Domain Access Control Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

reset value: unpredictable

Bits Access Description

31:0 Read / Write

Access permissions for all 16 domains - The meaning

of each field can be found in the ARM* Architecture

Reference Manual.

Table 16. Fault Status Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

X D 0 Domain Status

reset value: unpredictable

Bits Access Description

31:11 Read-unpredictable / Write-as-Zero Reserved

10 Read / Write

Status Field Extension (X)

This bit is used to extend the encoding of the Status field,

when there is a prefetch abort and when there is a data

abort. The definition of this field can be found in “Event

Architecture” on page 154

9Read / Write

Debug Event (D)

This flag indicates a debug event has occurred and that

the cause of the debug event is found in the MOE field of

the debug control register (CP14, register 10)

8 Read-as-zero / Write-as-Zero = 0

7:4 Read / Write

Domain - Specifies which of the 16 domains was being

accessed when a data abort occurred

3:0 Read / Write Status - Type of data access being attempted