Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

268 Order Number: 252480-006US

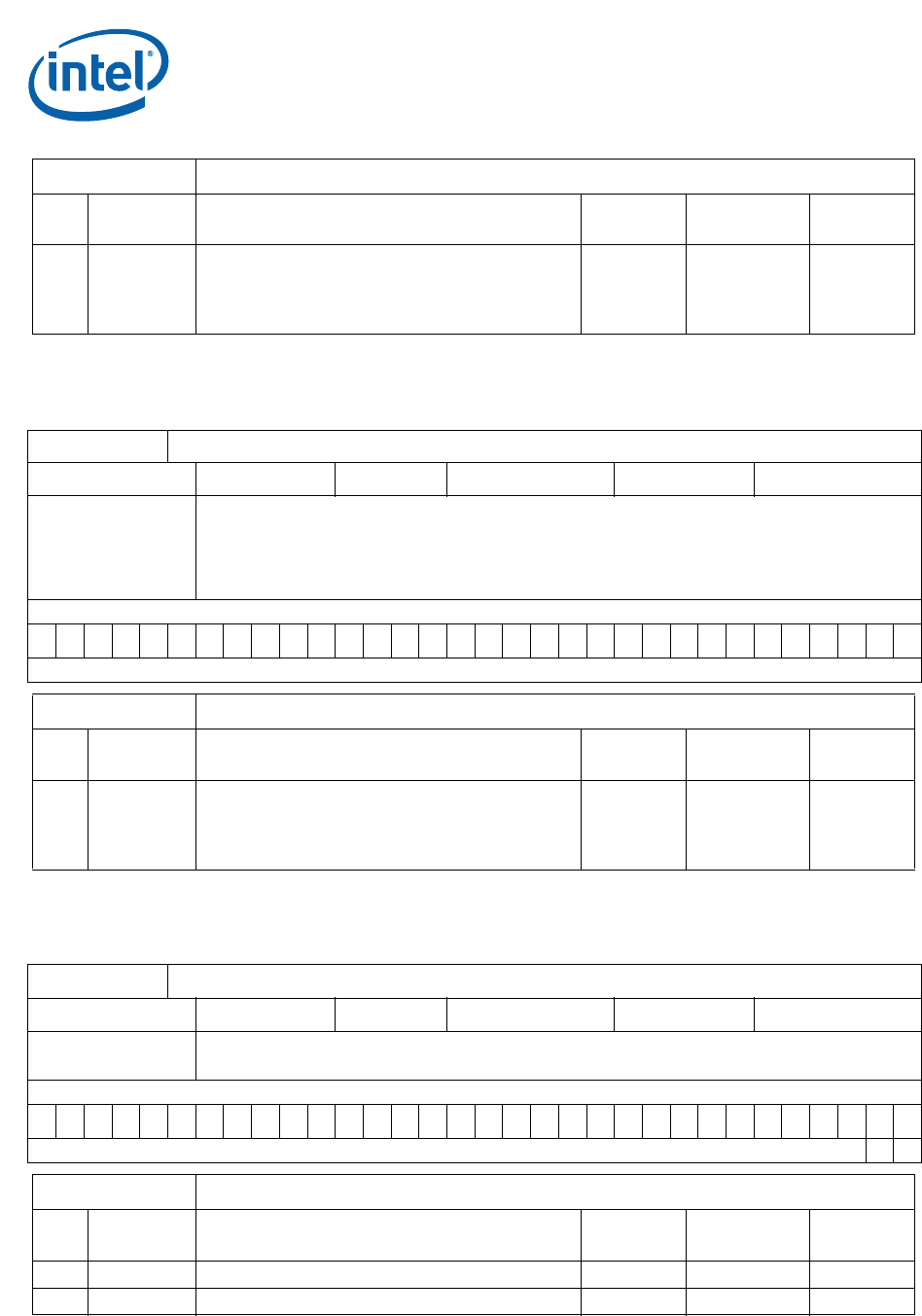

6.14.2.16 PCI Doorbell Register

(PCI_PCIDOORBELL)

6.14.2.17 AHB to PCI DMA AHB Address Register 0

(PCI_ATPDMA0_AHBADDR)

Register PCI_AHBDOORBELL

Bits Name Description

Reset

Value

PCI Access AHB Access

31:0 ADB

PCI generated doorbell interrupt to an AHB agent.

Normally read/write-1-to-set from PCI and read/

write-1-to-clear from AHB. Read/write from the AHB

side if Doorbell Test mode is enabled by setting

pci_csr.DBT to a 1.

0x00000000 RW1S

RW1C (RW if

pci_csr.DBT

=1)

Register Name: PCI_PCIDOORBELL

Hex Offset Address: 0xC000003C Reset Hex Value: 0x00000000

Register

Description:

The Intel XScale processor writes this register to generate an interrupt to an external PCI device on

PCI_INTA_N (INTA# on PCI). Any bit set to a 1 will generate the PCI interrupt if the PCI doorbell interrupt

is enabled (pci_inten.PDBEN = 1). This register is write-1-to-set from AHB and write-1-to-clear from PCI.

The Intel XScale processor writes a 1 to a bit or pattern of bits to generate the interrupt. The external

PCI device reads the register and writes 1(s) to clear the bit(s) and de-assert the interrupt. If the DBT

(Doorbell Test) bit is set in the pci_csr register, all bits become read/write from the AHB bus.

Access: See below.

31 0

PDB

Register

PCI_PCIDOORBELL

Bits Name Description

Reset

Value

PCI Access AHB Access

31:0 PDB

AHB generated doorbell interrupt to PCI. Normally

read/write-1-to-set from AHB and read/write-1-to-

clear from PCI. Read/write from the AHB side if

Doorbell Test mode is enabled by setting pci_csr.DBT

to a 1.

0x00000000 RW1C

RW1S (RW if

pci_csr.DBT

=1)

Register Name: PCI_ATPDMA0_AHBADDR

Hex Offset Address: 0xC0000040 Reset Hex Value: 0x00000000

Register

Description:

Source address on the AHB bus for AHB to PCI DMA transfers. Paired with pci_atpdma1_ahbaddr to allow

buffering of DMA transfer requests.

Access: See below.

31 210

address 0 0

Register

PCI_ATPDMA0_AHBADDR

Bits Name Description

Reset

Value

PCI Access AHB Access

31:2 address AHB word address 0x00000000 RO RW

1:0 Lower AHB address bits hard-wired to zero. 00 RO RO