Intel

®

IXP42X product line and IXC1100 control plane processors—Interrupt Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

404 Order Number: 252480-006US

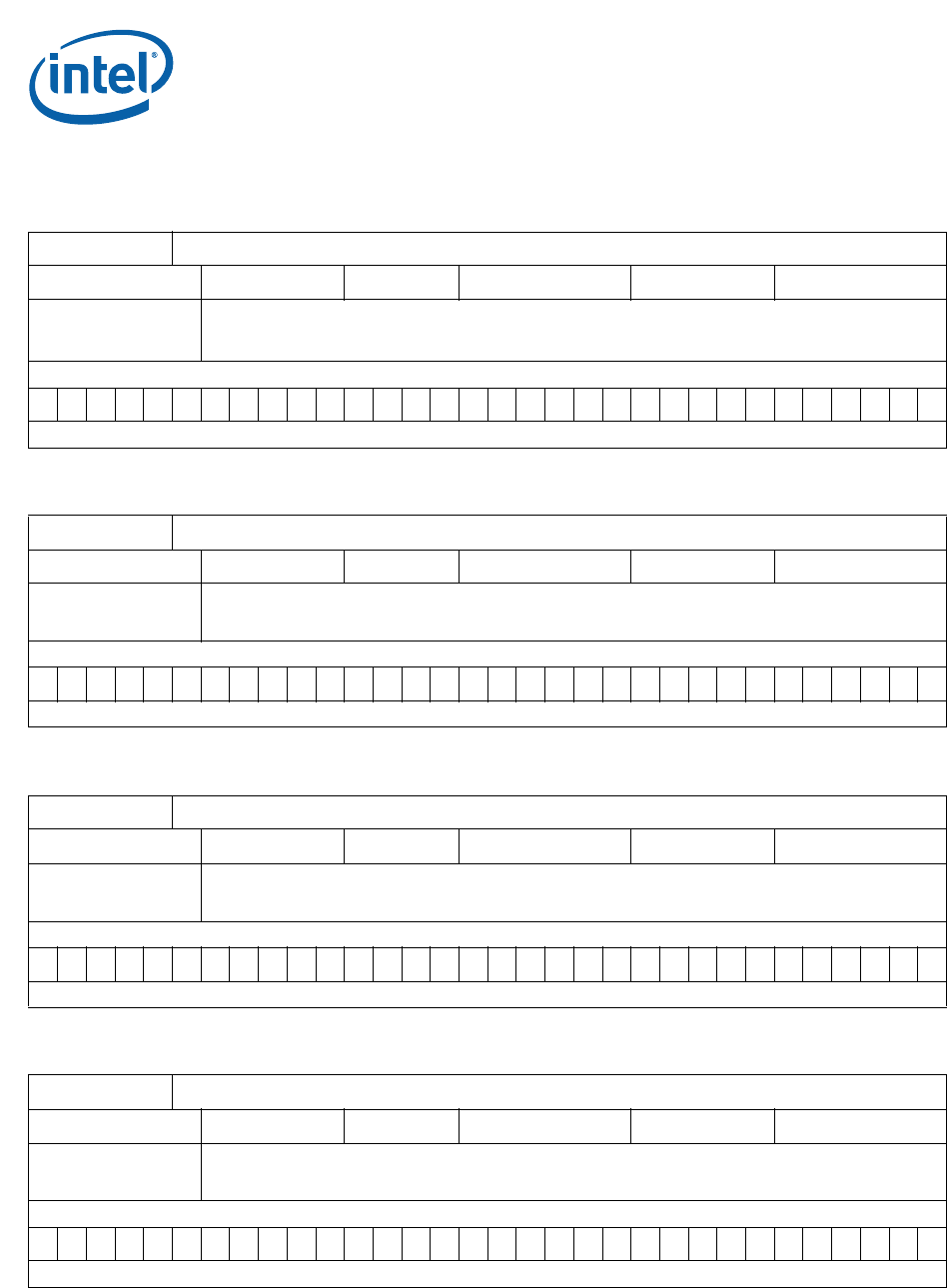

13.5.2 Interrupt-Enable Register

13.5.3 Interrupt Select Register

13.5.4 IRQ Status Register

13.5.5 FIQ Status Register

Register Name: INTR_EN

Hex Offset Address: 0xC800 3004 Reset Hex Value: 0x00000000

Register

Description:

Provides enables for the interrupts. This register allows the Intel XScale processor to disable interrupts

from selected blocks.

To enable an interrupt, a 1 is written into corresponding bit, to disable it, a 0 is written.

Access: Read/Write.

31 0

Interrupt Enables

Register Name: INTR_SEL

Hex Offset Address: 0xC800 3008 Reset Hex Value: 0x00000000

Register

Description:

This register decides if an interrupt is to be presented to the Intel XScale processor as an FIQ or an IRQ.

If a bit corresponding to an interrupt is set (to 1), that interrupt is presented as a FIQ. If the bit is reset

to 0, the interrupt is presented as an IRQ.

Access: Read/Write.

31 0

Interrupt Selects

Register Name: INTR_ IRQ_ST

Hex Offset Address: 0xC800 300C Reset Hex Value: 0x00000000

Register

Description:

This register is an “AND” of the incoming status with the INTR_EN and the inverted version of the

INTR_SEL. The IRQ_ST indicates which of the incoming interrupts are enabled as an IRQ. An Interrupt is

enabled if the corresponding bit is set, else it is disabled.

Access: Read.

31 0

IRQ Status Information

Register Name: INTR_FIQ_ST

Hex Offset Address: 0xC800 3010 Reset Hex Value: 0x00000000

Register

Description:

This register is an “AND” of the incoming status with the INTR_EN and the INTR_SEL. The IRQ_ST

indicates which of the incoming interrupts are enabled as a FIQ. An Interrupt is enabled if the

corresponding bit is set. Otherwise, it is disabled.

Access: Read.

31 0

FIQ Status Info