Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

96 Order Number: 252480-006US

An instruction breakpoint will generate a debug exception before the instruction at the

address specified in the ICBR executes. When an instruction breakpoint occurs, the

processor sets the DBCR.moe bits to 0b001.

Software must disable the breakpoint before exiting the handler. This allows the break-

pointed instruction to execute after the exception is handled.

Single step execution is accomplished using the instruction breakpoint registers and

must be completely handled in software (either on the host or by the debug handler).

3.6.6.2 Data Breakpoints

IXP42X product line and IXC1100 control plane processors’ debug architecture defines

two data breakpoint registers (DBR0, DBR1). The format of the registers is shown in

Table 36.

DBR0 is a dedicated data address breakpoint register. DBR1 can be programmed for

one of two operations:

• Data address mask

• Second data address breakpoint

The DBCON register controls the functionality of DBR1, as well as the enables for both

DBRs. DBCON also controls what type of memory access to break on.

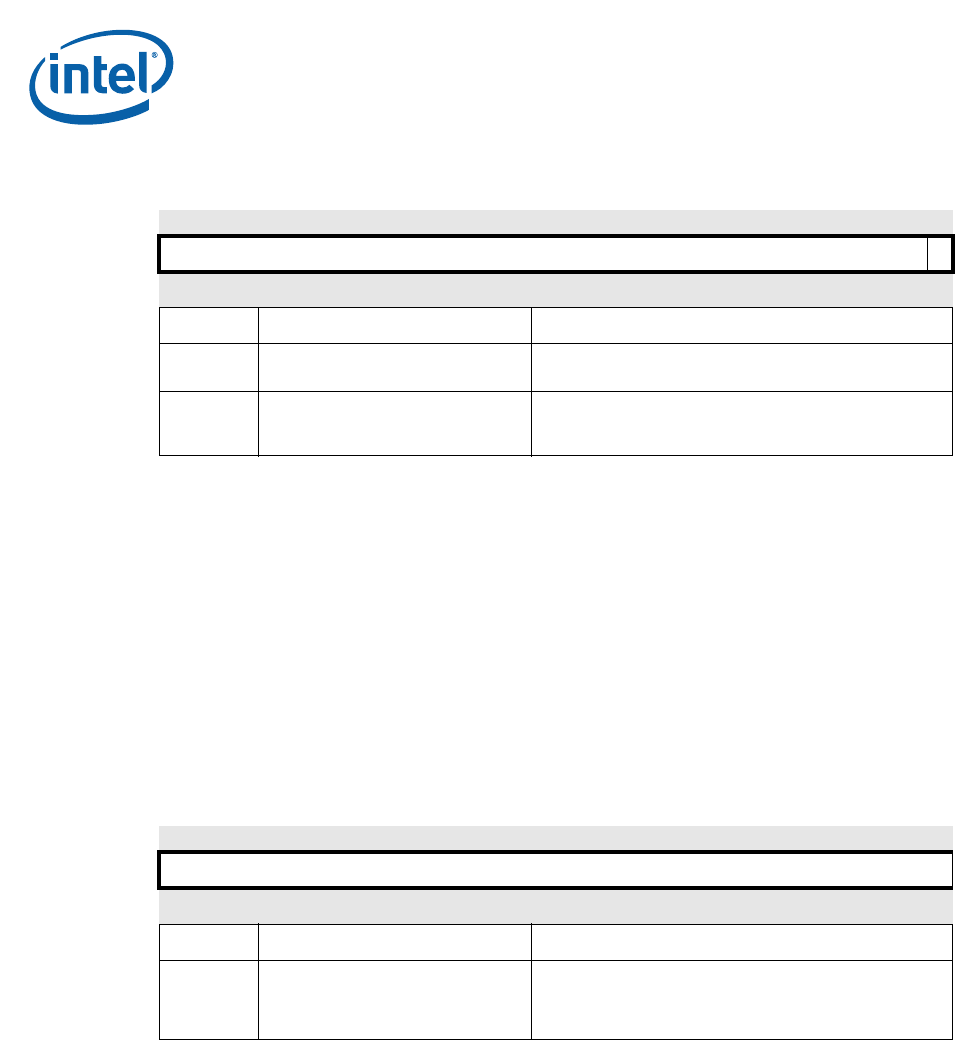

Table 35. Instruction Breakpoint Address and Control Register (IBCRx)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

IBCRx E

reset value: unpredictable address, disabled

Bits Access Description

31:1 Read / Write

Instruction Breakpoint MVA

in ARM mode, IBCRx[1] is ignored

0Read / Write

IBCRx Enable (E) -

0 = Breakpoint disabled

1 = Breakpoint enabled

Table 36. Data Breakpoint Register (DBRx)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DBRx

reset value: unpredictable

Bits Access Description

31:0 Read / Write

DBR0: Data Breakpoint MVA

DBR1:

Data Address Mask OR

Data Breakpoint MVA