Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 487

Universal Serial Bus (USB) v1.1 Device Controller—Intel

®

IXP42X product line and IXC1100

control plane processors

18.5.3.7 Bit 6 Reserved

Bit 6 is reserved for future use.

18.5.3.8 Transmit Short Packet (TSP)

The software uses the transmit short packet bit to indicate that the last byte of a data

transfer to the FIFO has occurred. This indicates to the UDC that a short packet or zero-

sized packet is ready to transmit.

Software must not set this bit if a 64-byte packet is to be transmitted. When the data

packet is successful transmitted, the UDC clears this bit.

18.5.4 UDC Endpoint 2 Control/Status Register (UDCCS2)

The UDC Endpoint 2 Control/Status Register contains seven bits that are used to

operate endpoint 2, a Bulk OUT endpoint.

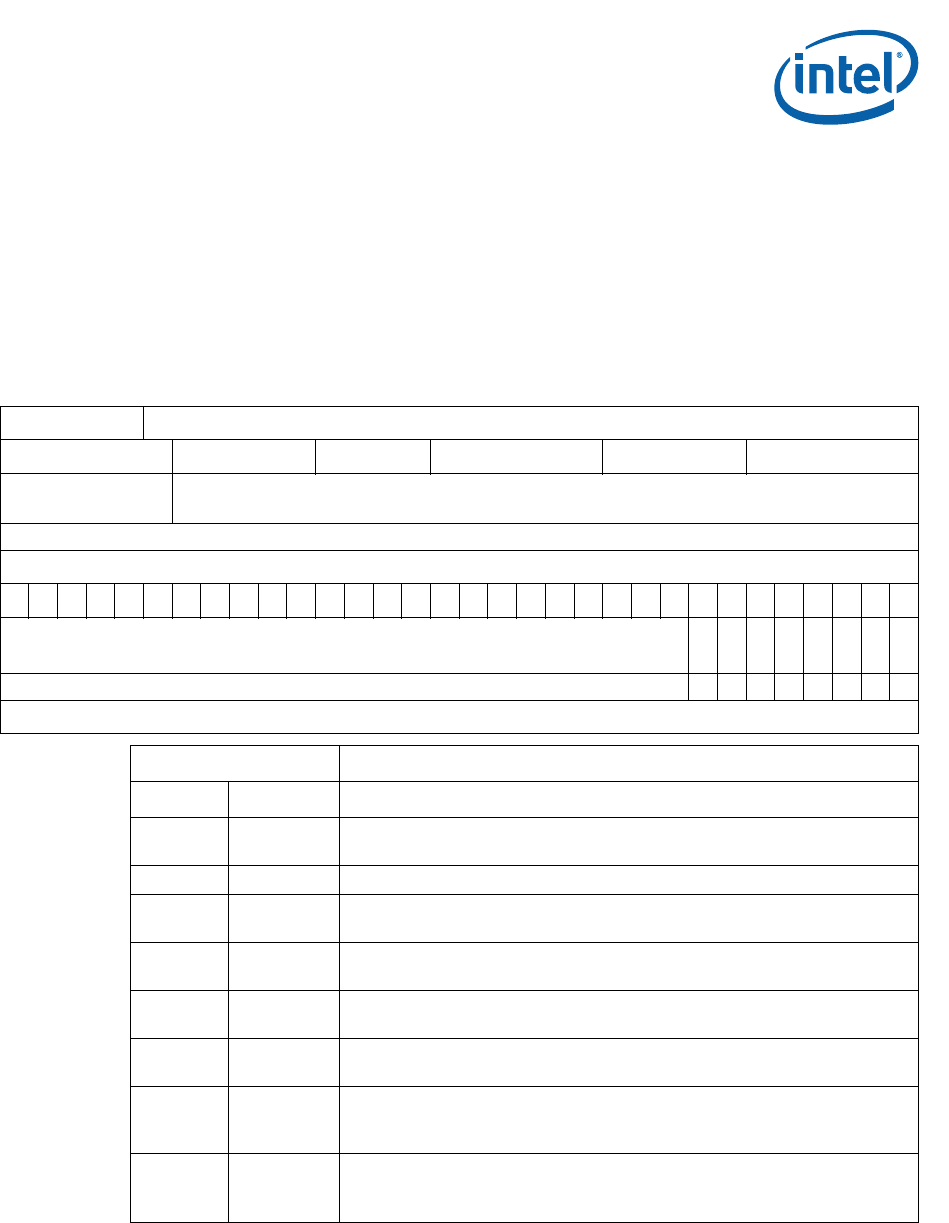

Register Name: UDCCS1

Hex Offset Address: 0 x C800B014 Reset Hex Value: 0 x 00000001

Register

Description:

Universal Serial Bus Device Controller Endpoint 1 Control and Status Register

Access: Read/Write

Bits

31 876543210

(Reserved)

TSP

(Rsvd)

FST

SST

TUR

FTF

TPC

TFS

X 00000001

Resets (Above)

Register

UDCCS1

Bits Name Description

7TSP

Transmit short packet (read/write 1 to set).

1 = Short packet ready for transmission.

6 (Reserved). Always reads 0.

5FST

Force STALL (read/write).

1 = Issue STALL handshakes to IN tokens.

4 SST

Sent STALL (read/write 1 to clear).

1 = STALL handshake was sent.

3TUR

Transmit FIFO underrun (read/write 1 to clear)

1 = Transmit FIFO experienced an underrun.

2FTF

Flush Tx FIFO (always read 0/ write a 1 to set).

1 = Flush Contents of TX FIFO

1TPC

Transmit packet complete (read/write 1 to clear).

0 = Error/status bits invalid.

1 = Transmit packet has been sent and error/status bits are valid.

0TFS

Transmit FIFO service (read-only).

0 = Transmit FIFO has no room for new data

1 = Transmit FIFO has room for at least 1 complete data packet