Intel

®

IXP42X product line and IXC1100 control plane processors—SDRAM Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

286 Order Number: 252480-006US

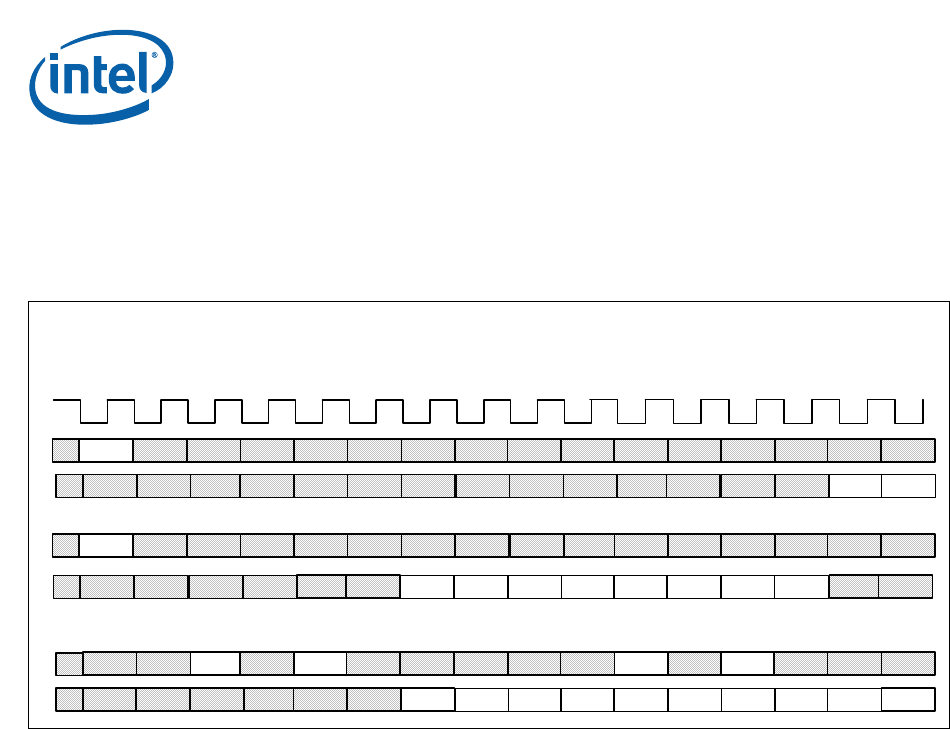

7.3.1.2 Read Burst Transfer (Interleaved AHB Reads)

The timing diagram in Figure 56 shows read requests from an NPE on the North AHB

and the Intel XScale processor on the South. Both masters access different memory

banks.

7.3.2 Write Transfer

The AHBs need to generate a write transaction with the address located in the SDRAM

space in order to initiate a write from SDRAM. One of the AHB Masters addresses the

SDRAM memory space. Upon detection of the write initiation, the control signal

performs an active cycle with the appropriate row address, followed with a RAS-to-CAS

delay.

After a RAS-to-CAS delay of a finite number of clocks (determined by the latency

setting – which has a default of three), the control signal generates a write command

and presents the column address. The SDRAM controller performs such writes until

either the end of the transfer on the AHB or until the column address increments to hit

a page crossover condition.

Upon such a crossover condition, the SDRAM Controller terminates the transaction by

performing a Burst Terminate followed by pre-charge cycle and resumes the read

transfer from the incremented address.

7.3.2.1 Write Transfer

The timing diagram in Figure 57 shows cycles on the SDRAM for a write cycle.

Figure 56. SDRAM Shared South AHB and North AHB Access

SDRAM COMMAND

AHBN ADDR

AHBN DATA

SDRAM CYCLE READ

CAS LATENCY = 2

Transaction on AHB1 and AHB0

clock

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

ADDR DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

ACTIVENOP READNOP NOP NOP

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

ACTIVE NOPNOP NOP READ NOP NOP NOPNOP

DONT

CARE

DONT

CARE

SDRAM

DATA

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

D0 AHBS

D1 AHBS D2 AHBS D3 AHBS D4 AHBS D5 AHBS D6 AHBS D7 AHBS D0 AHBN

D1 AHBN

AHBS ADDR

AHBS DATA

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

D0

ADDR DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

D1 D2 D3

DONT

CARE

D4 D5 D6 D7

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

NOP

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

D0 D1DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE

DONT

CARE