Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 459

High-Speed Serial Interfaces—Intel

®

IXP42X product line and IXC1100 control plane

processors

• Frame sync active level (high/low).

• MSb/LSb-first ordering for transmit and receive.

• Data polarity, maintain or invert.

• Select to use FBit (not data for T1) at frame start.

• Select value for idle timeslots on transmit and unused bit in 56k timeslots.

• Select buffer size.

• Configure lookup tables.

17.6.2 E1

E1 is a High-Speed Serial stream operating at 2.048 MHz. The stream is composed of

frames of which there are 8000 a second. Each frame consists of 32 slots, and each slot

is a byte in size. As there are 32 slots per frame, E1 can carry 32 channels. There are

no frame bits in this protocol.

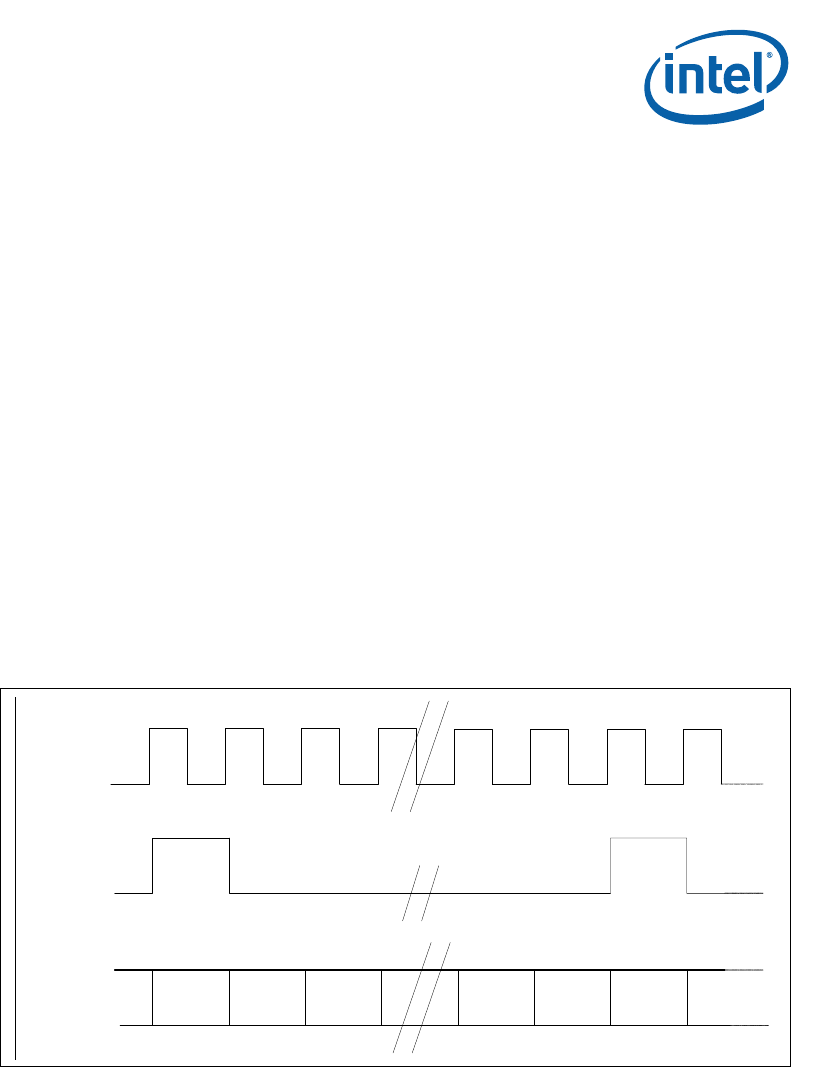

Figure 88 and Figure 89 illustrate a typical E1 frame with an active high frame sync

(level) and a positive edge clock for generating or sampling data. The HSS clock and

frame pulse can be programmed to be either HSS outputs or HSS inputs. An offset can

be programmed indicating when the TX frame is to be transmitted. The Polarity of the

received data and the level of the frame can also be programmed using the IxHssAcc

API.

Figure 88. E1 Transmit Frame

hss_t x_dat a

hss_t x_cl ock

hss_t x_f r ame

data 1 data 2 data 3 data 256data 255 data 1 data 2