Intel

®

IXP42X product line and IXC1100 control plane processors—SDRAM Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

290 Order Number: 252480-006US

These are the commands issued by the memory controller to the SDRAM and are not

accessible through the AHB (i.e. a master cannot issue these commands on the internal

bus to the memory controller unit).

§ §

4A1A0

0 0 0-1-2-3 0-1-2-3

0 1 1-2-3-0 1-0-3-2

1 0 2-3-0-1 2-3-0-1

1 1 3-0-1-2 3-2-1-0

8A2A1A0

0 0 0 0-1-2-3-4-5-6-7 0-1-2-3-4-5-6-7

0 0 1 1-2-3-4-5-6-7-0 1-0-3-2-5-4-7-6

0 1 0 2-3-4-5-6-7-0-1 2-3-0-1-7-6-5-4

0 1 1 3-4-5-6-7-0-1-2 3-2-1-0-7-6-5-4

1 0 0 4-5-6-7-0-1-2-3 4-5-6-7-0-1-2-3

1 0 1 5-6-7-0-1-2-3-4 5-4-7-6-1-0-3-2

1 1 0 6-7-0-1-2-3-4-5 6-7-5-4-2-3-0-1

1 1 1 7-0-1-2-3-4-5-6 7-6-5-4-3-2-1-0

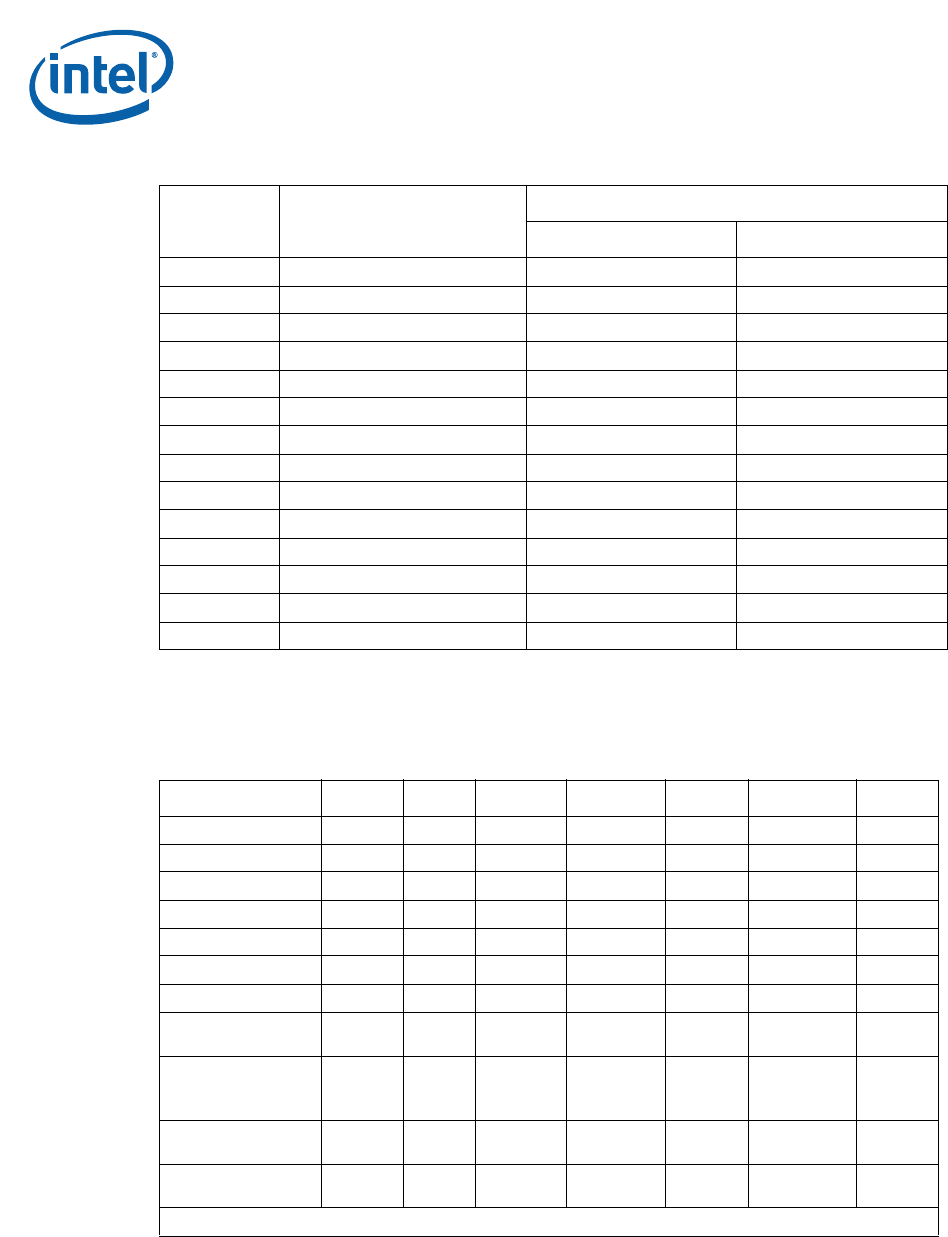

Table 115. SDRAM Burst Definitions

Burst Length Starting Column Address

Order of Accesses within a Burst

Type = Sequential Type = Interleaved

Table 116. SDRAM Commands

Command CS# RAS# CAS# WE# DQM ADDR DATA

COMMAND INHIBIT H X X X X X

NO OPERATION L H H H X X

ACTIVE L L H H X Bank/Row

*

READ L H L H X Bank/Col

WRITE L H L L X Bank/Col VALID

BURST TERMINATE L H H L X X ACTIVE

PRECHARGE L L H L X CODE

AUTO REFRESH OR

SELF REFRESH

LL L H X X

LOAD MODE

REGISTER

LL L L X

BA = 00

ADDR =

opcode

WRITE ENABLE/

OUTPUT ENABLE

-- - - L -ACTIVE

WRITE INHIBIT/

OUTPUT HIGH-Z

-- - - H -HIGH-Z

Note: Bank is used in the “SDRAM” sense, synonymous to LEAF in the rest of the documentation.