Intel

®

IXP42X product line and IXC1100 control plane processors—Ethernet MAC A

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

430 Order Number: 252480-006US

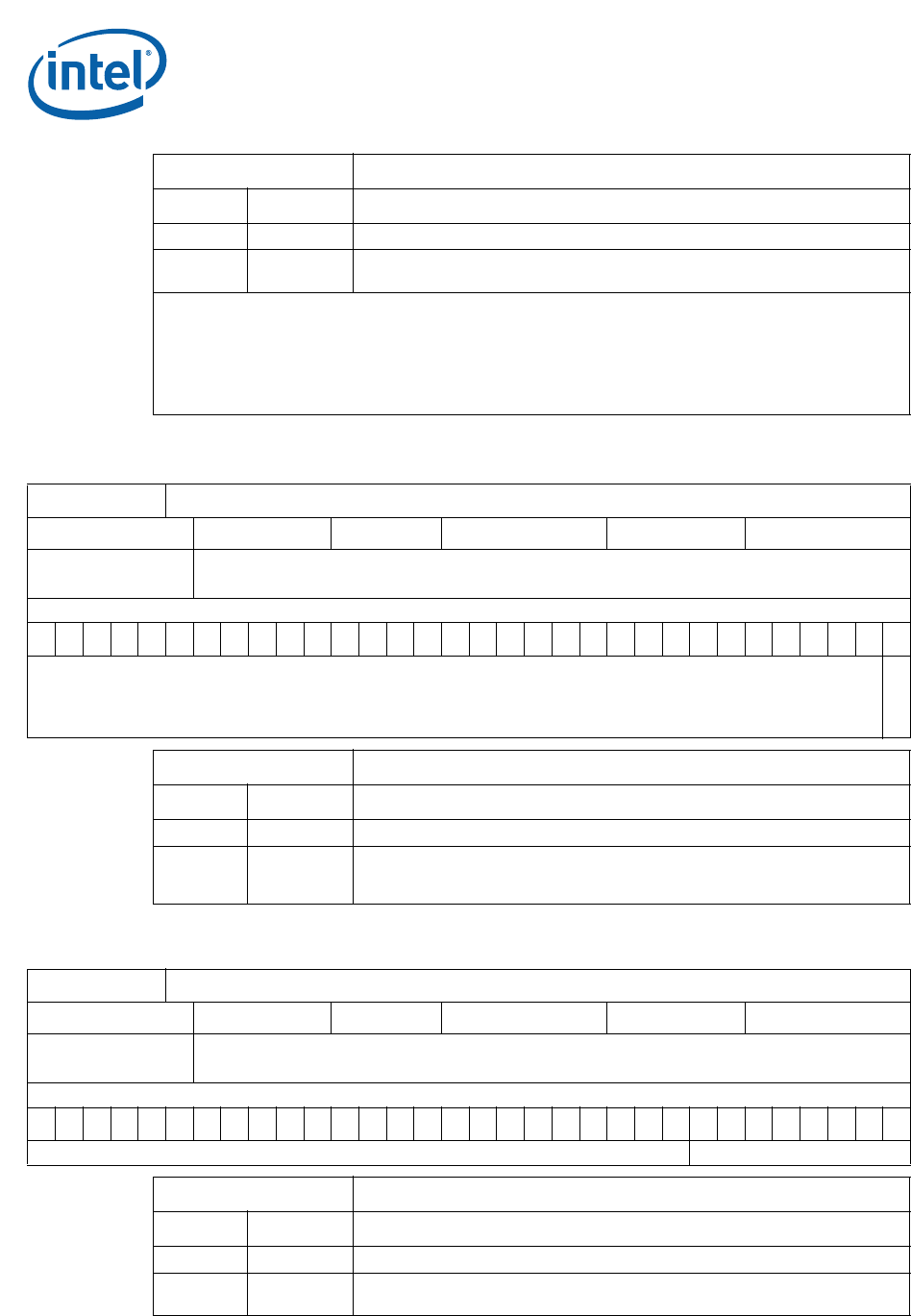

15.2.4 Receive Control 2

15.2.5 Random Seed

1 Pad strip 1 = Causes the pad bytes to be stripped from receive data.

0

Receive

enable

1 = Causes reception to be enabled.

Notes: Broadcast packets will only be dropped if the following three conditions are met.

1. “Broadcast Disable” bit,“b7=1”.

2. The Address M ask register is NOT 00 00 00 00 00 00.

3. “Address Filter Enable” bit, “b5=1”.

Setting the address mask register to all 00 (i.e., don’t care about the address) and setting the Broadcast

Disable bit to “b7=1” will not prevent packets from being accepted. Broadcast packets will continue to be

received. All three conditions shown above must be satisfied to stop receiving packets.

Register Name: rxctrl2

Hex Offset Address: 0xC8009014 Reset Hex Value: 0x00000000

Register

Description:

Receive Control Register Two

Access: Read/Write.

31 10

(Reserved)

RX DEF EN

Register rxctrl2

Bits Name Description

31:1 (Reserved)

0

Receive

deferral

enable

1 = Enables receive deferral checking.

Register Name: rndmseed

Hex Offset Address: 0xC8009020 Reset Hex Value: 0x00000000

Register

Description:

Random Seed Register

Access: Read/Write.

31 87 0

(Reserved) Random Seed

Register rndmseed

Bits Name Description

31:8 (Reserved)

7:0

Random

Seed

Random seed used for LFSR initialization in the back-off block.

Register rxcrtl1 (Sheet 2 of 2)

Bits Name Description