©2008 Advanced Micro Devices, Inc.

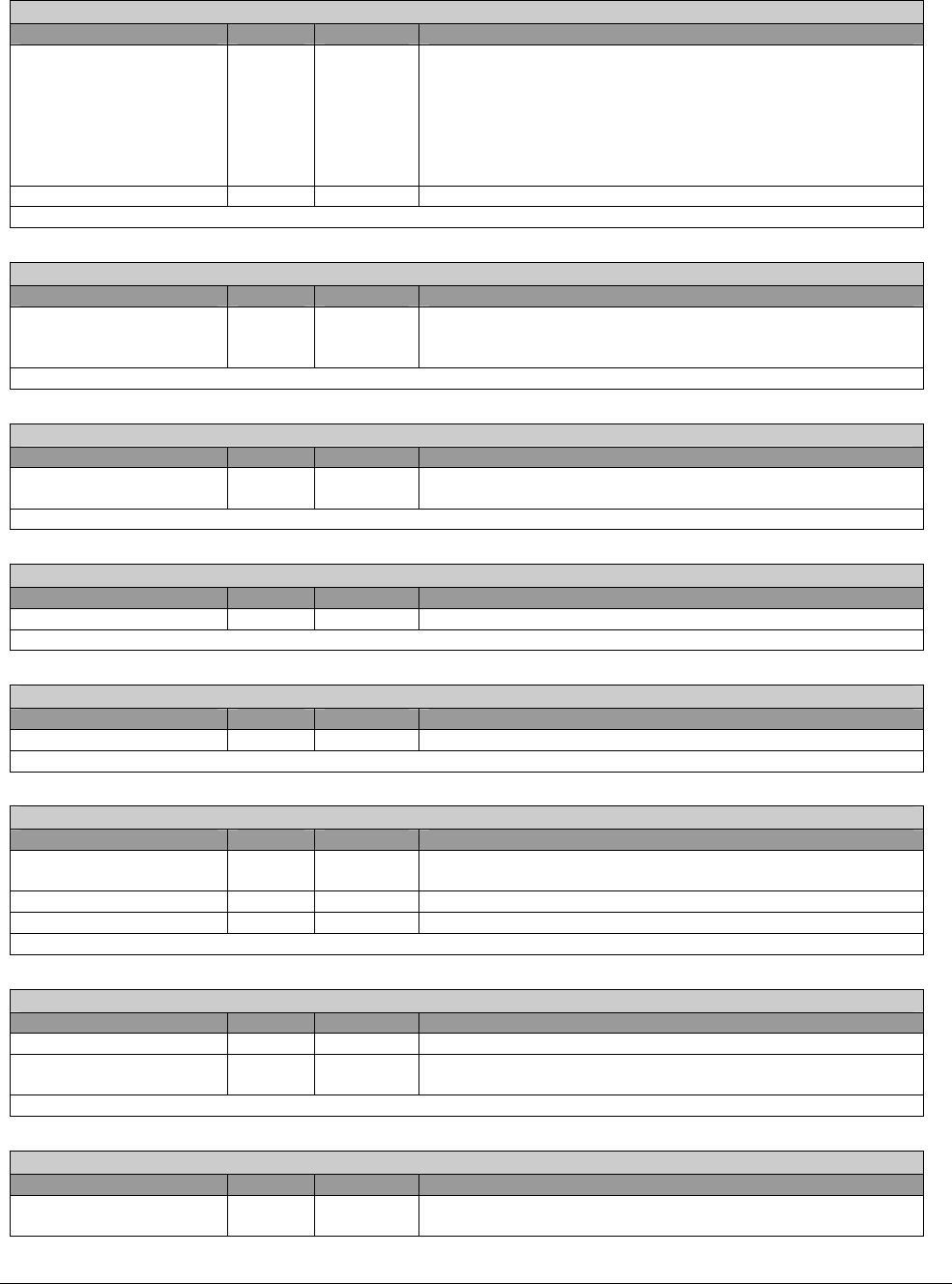

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 100

Revision ID/Class Code- R - 32 bits - [PCI_Reg: 08h]

Field Name Bits Default Description

RevisionID 7:0 11h /

12h /

13h

This field reflects the ASIC revision.

11h : For ASIC revision A11

12h : For ASIC revision A12

13h : For ASIC revision A13

For ASIC revisions after A13, by default this field will read 13h

still. However, if SMBUS PCI config 70h bit 8 is set to 1, a

hidden revision ID can be read from this field.

Class Code 31:8 0C0500h 0C0500h denotes a SMBUS controller.

Revision ID/Class Code register

Cache Line Size- R - 8 bits - [PCI_Reg: 0Ch]

Field Name Bits Default Description

Cache Line Size 7:0 00h This register specifies the system cacheline size. This module

does not use Memory Write and Invalidate command and so

this register is not applicable. It is hardcoded to 0.

Cache line size register

Latency Timer- R - 8 bits - [PCI_Reg: 0Dh]

Field Name Bits Default Description

Latency Timer 7:0 00h This register specifies the value of the Latency Timer. This is

not used in this module and so it is always 0.

Latency timer register

Header Type- R - 8 bits - [PCI_Reg: 0Eh]

Field Name Bits Default Description

Header Type 7:0 80h This device is a multifunction device.

Header type register

BIST- R - 8 bits - [PCI_Reg: 0Fh]

Field Name Bits Default Description

BIST 7:0 00h The module has no built-in self-test and so this is always 0.

BIST register

Base Address 0- R - 32 bits - [PCI_Reg: 10h]

Field Name Bits Default Description

IO/Memory 0 1b 1 = IO

0 = Memory

Reserved 3:1 000b

SmBusBaseAd 31:4 0000000h SMBus Base Address

Base Address 0 register

Base Address 1- R - 32 bits - [PCI_Reg: 14h]

Field Name Bits Default Description

Reserved 9:0 000h Hardwired to 0; memory map only

MultiMediaTimerBaseAd

dr

31:10 000000h High Precision Event Timer (also called Multi-media Timer)

base address.

Base Address 1 register

Base Address 2- R - 32 bits - [PCI_Reg: 18h]

Field Name Bits Default Description

Base Address 2 31:0 0000_000

0h

Not used and is hardcoded to 0.