©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual Proprietary Page 229

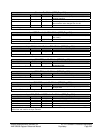

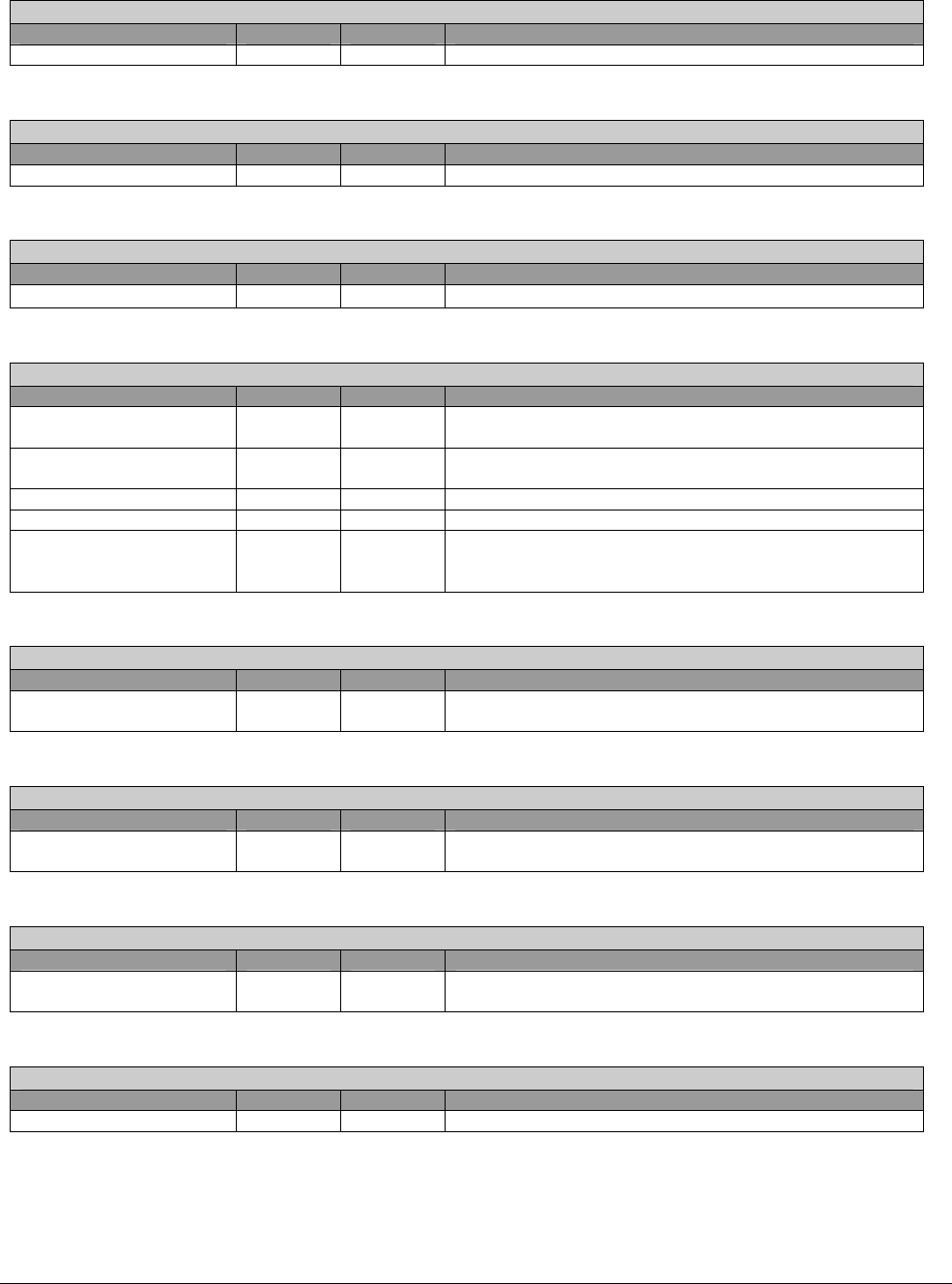

Latency Timer – R – 8 bits – [PCI_Reg: 0Dh]

Field Name Bits Default Description

Latency Timer 7:0 00h Hardwired to “0”.

Header Type – R – 8 bits – [PCI_Reg: 0Eh]

Field Name Bits Default Description

Header Type 7:0 00h Hardwired to “0”.

BIST – R – 8 bits – [PCI_Reg: 0Fh]

Field Name Bits Default Description

BIST

15:0 0000h Hardwired to “0”

.

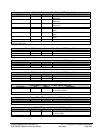

Lower Base Address Register – RW – 32 bits – [PCI_Reg: 10h]

Field Name Bits Default Description

Space Type 0 0b Hardwired to “0” to indicate this BAR is located in memory

space only.

Address Range 2:1 10b Hardwired to 10b to indicate this BAR can be located

anywhere in 64-bit address space.

Prefetchable 3 0b Hardwired to “0” to indicate this BAR is not prefetchable.

Reserved 13:4 000h Hardwired to “0”.

Lower Base Address 31:14 00000h Lower Base Address for the HD Audio controller’s memory

mapped configuration registers. 16K bytes are requested

by hardwiring bits[13:4] to 0.

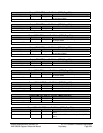

Upper Base Address Register – RW – 32 bits – [PCI_Reg: 14h]

Field Name Bits Default Description

Upper Base Address 31:0 00000000

h

Upper Base Address for the HD Audio controller’s memory

mapped configuration registers.

Subsystem Vendor ID – RW – 16 bits – [PCI_Reg: 2Ch]

Field Name Bits Default Description

Subsystem Vendor ID 15:0 0000h This register is implemented as write-once register. Any

subsequent writes have no effect.

Subsystem ID – RW – 16 bits – [PCI_Reg: 2Dh]

Field Name Bits Default Description

Subsystem ID 15:0 0000h This register is implemented as write-once register. Any

subsequent writes have no effect.

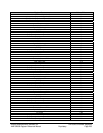

Capabilities Pointer – R – 8 bits – [PCI_Reg: 34h]

Field Name Bits Default Description

Capabilities Pointer 7:0 50h This register indicates the offset for the capability pointer