©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 123

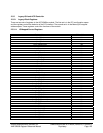

2.3.2 SMBus Registers

Register Name Offset Address

SMBusStatus 00h

SMBusSlaveStatus 01h

SMBusControl 02h

SMBusHostCmd 03h

SMBusAddress 04h

SMBusData0 05h

SMBusData1 06h

SMBusBlockData 07h

SMBusSlaveControl 08h

SMBusShadowCmd 09h

SMBusSlaveEvent 0A-0Bh

SlaveData 0C-0Dh

SMBusTiming 0Eh

Note: The SMBus registers are located at the IO memory space base address defined by PCI configuration

register 90-93h

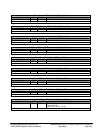

SMBusStatus - RW - 8 bits - [SMBUS:00h]

Field Name Bits Default Description

HostBusy 0 0b This bit indicates the SMBus controller is in the process of

completing a command. When this bit is set, software should

not access any other SMBus registers [Read-only]

SMBusInterrupt 1 0b This bit is set by hardware to indicate the completion of the last

host command. This bit can be cleared by writing an 1 to it.

DeviceErr 2 0b This bit is set by hardware to indicate an error of one of the

following: 1) illegal command field, 2) unclaimed cycle, 3) host

device time-out. This bit can be cleared by writing an 1 to it.

BusCollision 3 0b This bit is set by hardware to indicate SMBus transaction

collision; this bit can be cleared by writing an 1 to it.

Failed 4 0b This bit is set by hardware to indicate a failed bus transaction,

set when SMBusControl.Kill bit is set. This bit is cleared by

writing an 1 to it

Reserved 7:5 000b

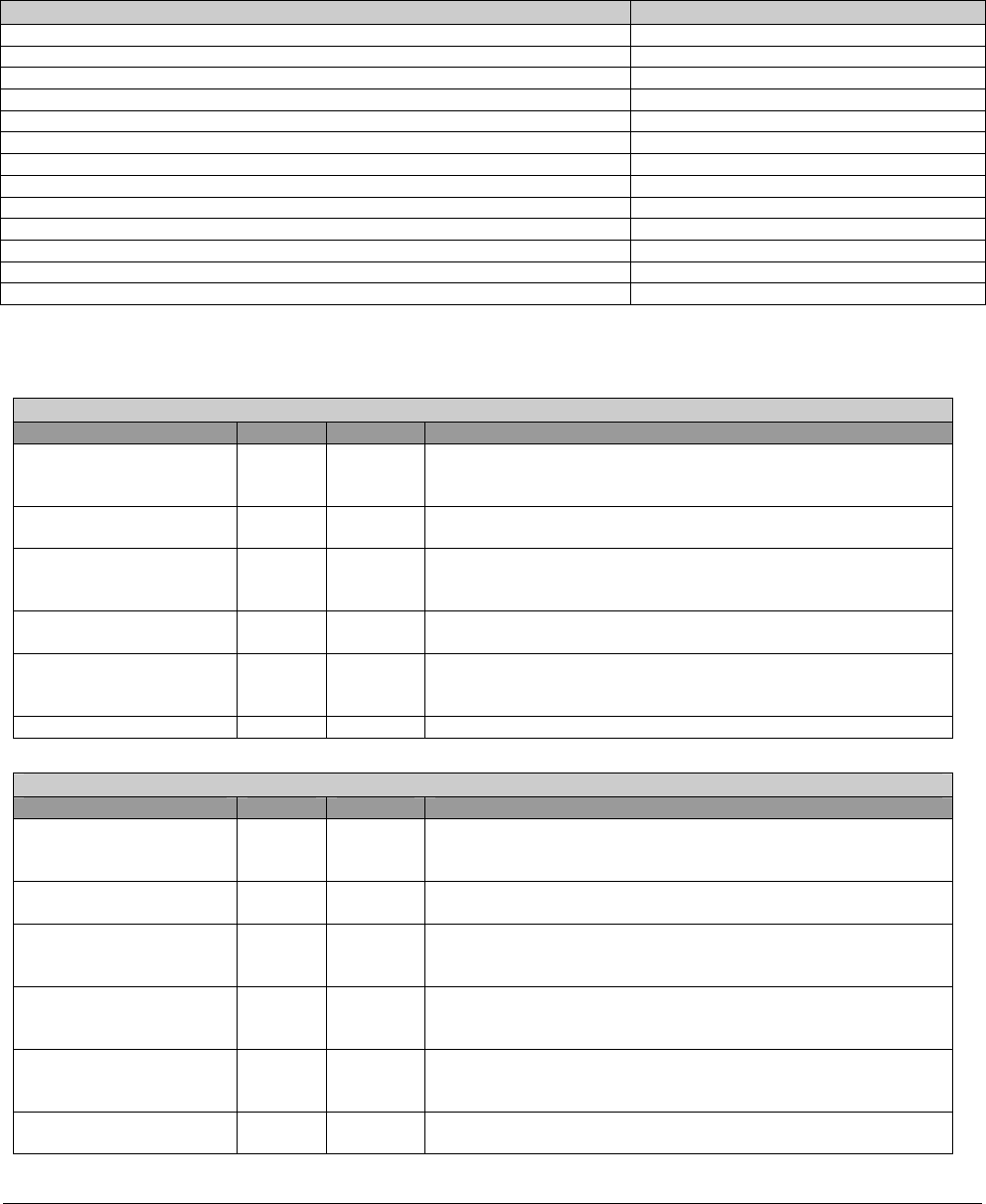

SMBusSlaveStatus - RW - 8 bits - [SMBUS:01h]

Field Name Bits Default Description

SlaveBusy 0 0b This bit indicates the SMBus controller slave interface is in the

process of receiving data. Software should not try to access

any other SMBus register when this bit is set. [Read-only]

SlaveInit 1 0b Writing a 1 to this bit will initialize the slave. It is unnecessary to

write it back to 0. A read from it will always return a 0.

SlaveStatus 2 0b This bit is set by hardware to indicate a slave cycle event match

of the SMBus slave command and SMBus Slave Event match.

This bit can be cleared by writing an 1 to it.

Shadow1Status 3 0b This bit is set by hardware to indicate a slave cycle address

match of the SMB_Shadow1 port. This bit can be cleared by

writing a 1 to it.

Shadow2Status 4 0b This bit is set by hardware to indicate a slave cycle address

match of the SMB_Shadow2 port. This bit can be cleared by

writing a 1 to it.

AlertStatus 5 0b This bit is set by hardware to indicate SMBALERT_ signal. This

function is not supported. [Read-only]