©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 53

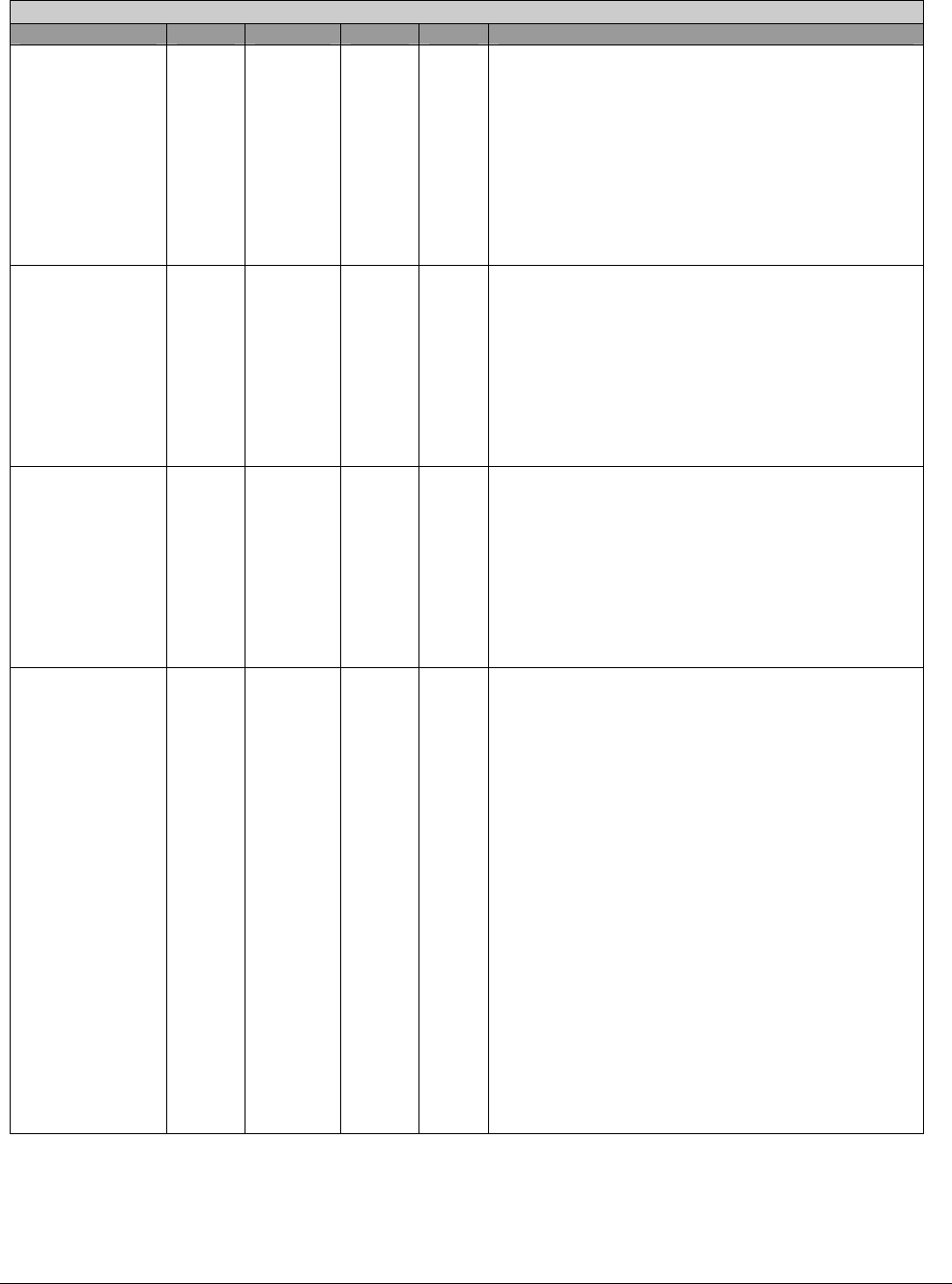

HcControl - 32 bits - [MEM_Reg : 04h]

Field Name Bits Default HCD HC Description

IE 3 0b RW R

IsochronousEnable

This bit is used by HCD to enable/disable processing

of isochronous Eds. While processing the periodic list

in a Frame, HC checks he status of this bit when it

finds an Isochronous ED (F=1). If set (enabled), HC

continues processing the Eds. If cleared (disabled),

HC halts processing of the periodic list (which now

contains only isochronous Eds) and begins

processing the Bulk/Control lists. Setting this bit is

guaranteed to take effect in the next Frame (not the

current Frame).

CLE 4 0b RW R

ControlListEnable

This bit is set to enable the processing of the Control

list in the next Frame. If cleared by HCD, processing

of the Control list does not occur after the next SOF.

HC must check this bit whenever it determines to

process the list. When disabled, HCD may modify the

list. If HcControlCurrentED is pointing to an ED to be

removed, HCD must advance the pointer by updating

HcControlCurrentED before re-enabling processing of

the list.

BLE 5 0b RW R

BulkListEnable

This bit is set to enable the processing of the Bulk list

in the next Frame. If cleared by HCD, processing of

the Bulk list does not occur after the next SOF. HC

checks this bit whenever it determines to process the

list. When disabled, HCD may modify the list. If

HcBulkCurrentED is pointing to an ED to be removed,

HCD must advance the pointer by updating

HcBulkCurrentED before re-enabling processing of

the list.

HCFS 7:6 00b RW RW

HostControllerFunctionalState for USB

00b: U

SBRESET

01b: USBRESUME

10b: USBOPERATIONAL

11b: USBSUSPEND

A transition to USBOPERATIONAL from another

state causes SOF generation to begin 1 ms

later. HCD may determine whether HC has

begun sending SOFs by reading the

StartofFrame field of HcInterruptStatus.

This field may be changed by HC only when in

the U

SBSUSPEND state. HC may move from the

USBSUSPEND state to the USBRESUME state after

detecting the resume signaling from a

downstream port.

HC enters U

SBSUSPEND after a software reset,

whereas it enters U

SBRESET after a hardware

reset. The latter also resets the Root Hub and

asserts subsequent reset signaling to

downstream ports.