©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 103

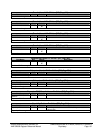

DmaLimit- RW - 8 bits - [PCI_Reg: 42h]

Field Name Bits Default Description

DmaBurstLimit 6:0 00h Enables the amount of burst data the legacy DMA engine can

sustain before it should give up the internal bus.

DmaLimitEnable 7 0h This is another enhancement to the legacy DMA engine. In

the original design, certain DMA request (such as Infrared) will

cause the legacy DMA engine to dominate the internal bus for

a very long time (up to 512 bytes) and thereby causing long

latency for other devices. Setting this bit will cause the legacy

DMA engine to limit its transfer per burst based on bits [6:0]

DmaLimit register

DmaPrefetchEnable RW - 8 bits - [PCI_Reg: 43h]

Field Name Bits Default Description

DmaPrefetchEnable 0 1b Legacy read DMA prefetch function enable.

1 – Enable

0 – Disable

When set, the DMA engine will keep the data inside the FIFO,

even though the requesting device has deasserted the DMA

request. When the device requests data again, the DMA

engine will have data available instead of having to fetch data

from the memory again. Note this enhancement only applies to

channel 0, 1, 2, and 3. It has no effect on channel 5, 6, or 7

Reserved 7:1 00h

DmaPrefetchEnable register

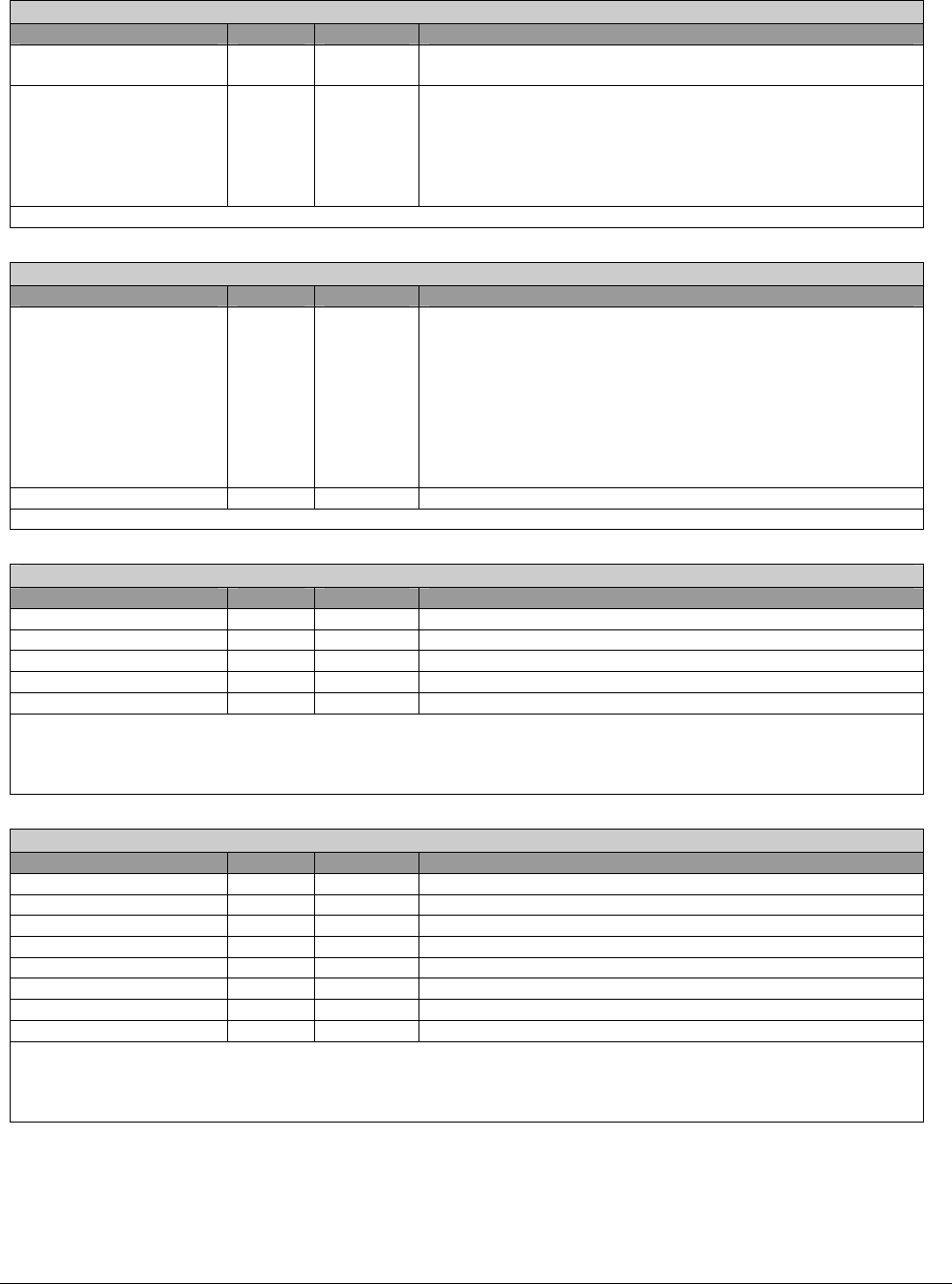

ISA Address Decode Control Register #1- RW - 8 bits - [PCI_Reg: 48h]

Field Name Bits Default Description

Window 0 0 1b 896K to 960K PCI enable

Window 1 1 1b 640K to 768K PCI enable

Window 2 2 1b 512K to 640K PCI enable

Window 3 3 1b 0K to 512K PCI enable

Reserved 7:4 0h

ISA Address Decode Control Register #1: This register defines the enable bits for four memory segments. If the

enable bit is set to 1, an ISA master or DMA access to the memory segment associated with that bit is forwarded to

the internal bus. The SB600 does not have any ISA master, because the bus is internal; however, it may affect

DMA transfers with the LPC module. Software should set all these bits to 1's.

ISA Address Decode Control Register #2- RW - 8 bits - [PCI_Reg: 49h]

Field Name Bits Default Description

Window 0 0 1b C0000h to C3FFFh

Window 1 1 1b C4000h to C7FFFh

Window 2 2 1b C8000h to CBFFFh

Window 3 3 1b CC000h to CFFFFh

Window 4 4 1b D0000h to D3FFFh

Window 5 5 1b D4000h to D7FFFh

Window 6 6 1b D8000h to DBFFFh

Window 7 7 1b DC000h to DFFFFh

ISA Address Decode Control Register #1: This register defines the PCI enable bits for four memory segments. If

the enable bit is set to 1, an ISA master or DMA access to the memory segment associated with that bit is forward

to the internal bus. The SB600 does not have any ISA master, because the bus is internal; however, it may affect

the DMA transfers with the LPC module. Software should set all these bits to 1's.