©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 84

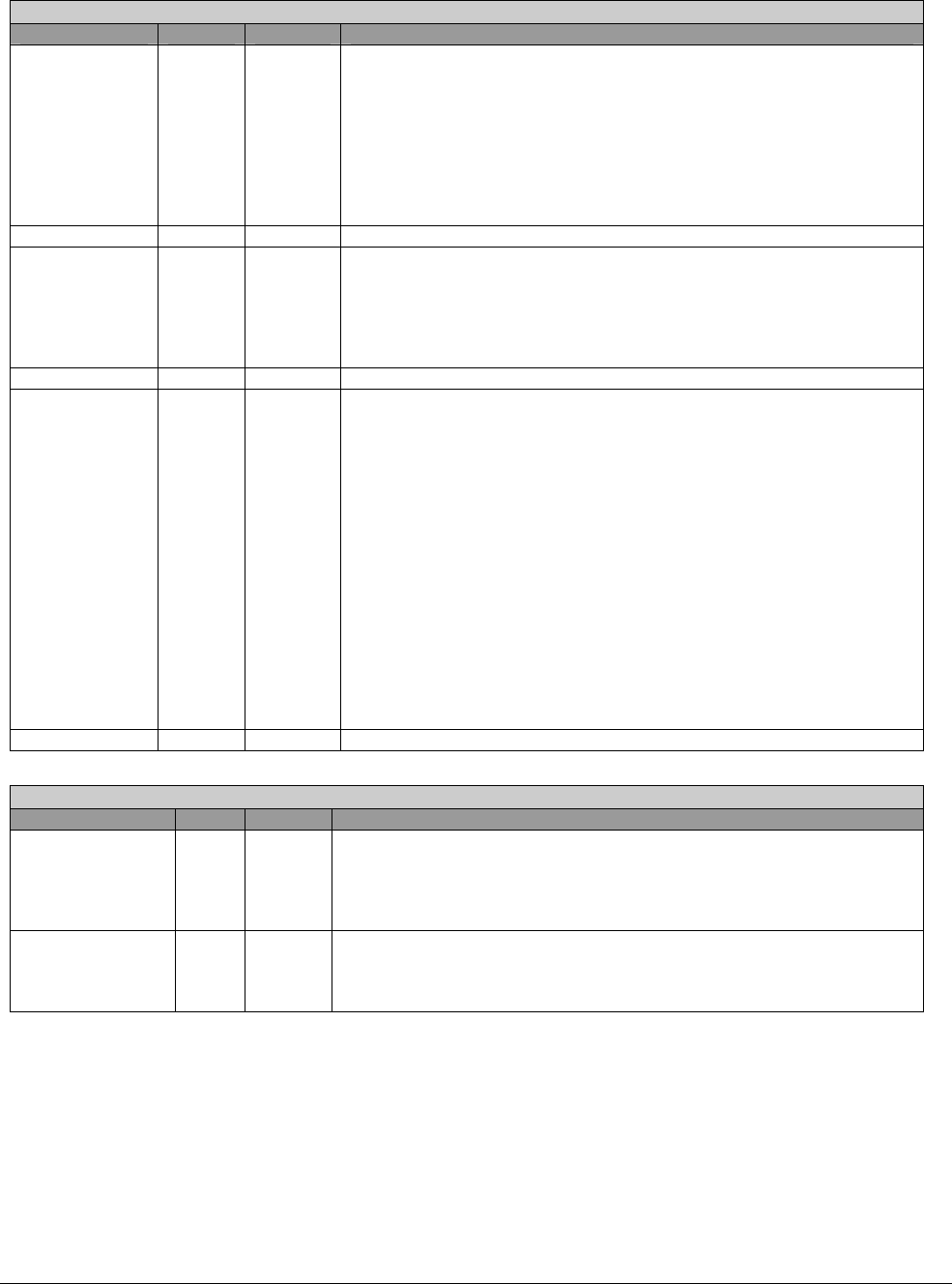

USBCMD – RW - 32 bits - [EOR_Reg : EHCI_EOR + 00h]

Field Name Bits Default Description

Asynchronous

Schedule Park

Mode Count

(Optional)

9:8 00b If the Asynchronous Park Capability bit in the HCCPARAMS register is a

one, then this field defaults to 3h and is R/W. Otherwise it defaults to

zero and is RO. It contains a count of the number of successive

transactions the host controller is allowed to execute from a high-speed

queue head on the Asynchronous schedule before continuing traversal

of the Asynchronous schedule. Valid values are 1h to 3h. Software

must not write a zero to this bit when Park Mode Enable is a one as this

will result in undefined behavior.

[Read/Write or Read-only]

Reserved 10 This bit is reserved and should be set to Zero.

Asynchronous

Schedule Park

Mode Enable

(Optional)

11 0b [Read-only]

If the Asynchronous Park Capability bit in the HCCPARAMS register is a

one, then this bit defaults to a 1h and is R/W. Otherwise the bit must be

a zero and is RO. Software uses this bit to enable or disable Park mode.

When this bit is one, Park mode is enabled. When this bit is a zero, Park

mode is disabled.

Reserved 15:12 This bit is reserved and should be set to Zero.

Interrupt

Threshold

Control

23:16 08h This field is used by system software to select the maximum rate at

which the host controller will issue interrupts. The only valid values are

defined below. If software writes an invalid value to this register, the

results are undefined.

00h = Reserved

01h = 1 micro-frame

02h = 2 micro-frames

04h = 4 micro-frames

08h = 8 micro-frames (default, equates to 1 ms)

10h = 16 micro-frames (2 ms)

20h = 32 micro-frames (4 ms)

40h = 64 micro-frames (8 ms)

Any other value in this register yields undefined results. Software

modifications to this bit while HCHalted bit is equal to zero results in

undefined behavior.

Reserved 31:24 These bits are reserved and should be set to Zeros.

USBSTS - RW - 32 bits - [EOR_Reg : EHCI_EOR + 04h]

Field Name Bits Default Description

USBINT 0 0b USB Interrupt. The Host Controller sets this bit to 1 on the completion of

a USB transaction, which results in the retirement of a Transfer Descriptor

that had its IOC bit set. The Host Controller also sets this bit to 1 when a

short packet is detected (actual number of bytes received was less than

the expected number of bytes).

USBERRINT 1 0b USB Error Interrupt . The Host Controller sets this bit to 1 when

completion of a USB transaction results in an error condition (e.g., error

counter underflow). If the TD on which the error interrupt occurred also

had its IOC bit set, both this bit and USBINT bit are set.