©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 30

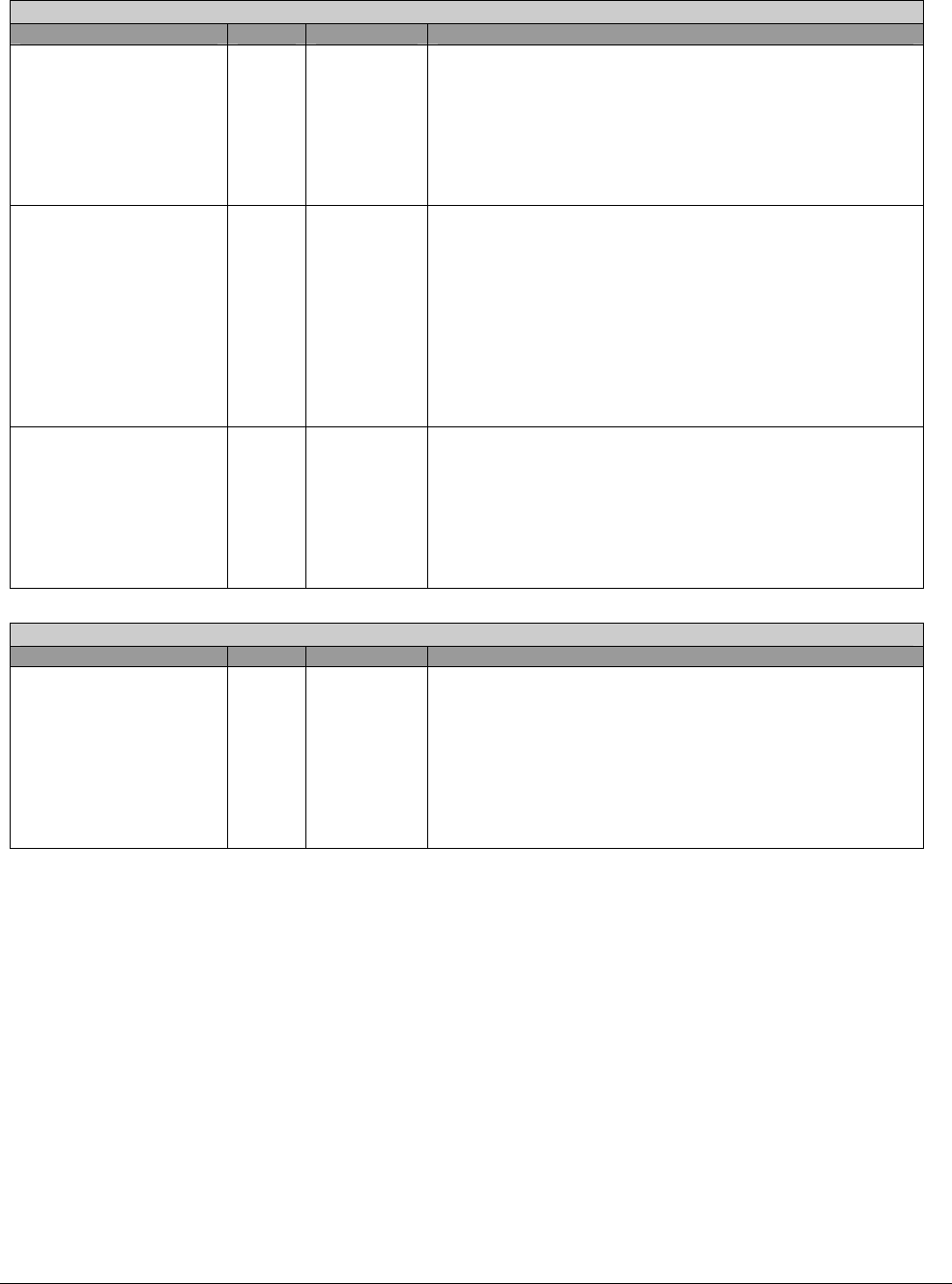

Command Completion Coalescing Control(CCC_CTL) - RW – 32 bits [Mem_reg: ABAR + 14h]

Field Name Bits Default Description

CCC Interrupt (INT) 7:3 1Fh Read Only

Specifies the interrupt used by the CCC feature. This

interrupt must be marked as unused in the Ports

Implemented (PI) register by the corresponding bit being set

to ‘0’. Thus, the CCC interrupt corresponds to the interrupt

for an unimplemented port on the controller. When a CCC

interrupt occurs, the IS.IPS[INT] bit shall be asserted to ‘1’.

This field also specifies the interrupt vector used for MSI.

Command Completions

(CC)

15:8 01h Specifies the number of command completions that are

necessary to cause a CCC interrupt. The HBA has an

internal command completion counter, hCccComplete.

hCccComplete is incremented by one each time a selected

port has a command completion. When hCccComplete is

equal to the command completions value, a CCC interrupt is

signaled. The internal command completion counter is reset

to ‘0’ on the assertion of each CCC interrupt. A value of ‘0’

for this field shall disable CCC interrupts being generated

based on the number of commands completed, i.e. CCC

interrupts are only generated based on the timer in this case.

Timeout Value (TV) 31:16 0001h The timeout value is specified in 1 millisecond intervals. The

timer accuracy shall be within 5%. hCccTimer is loaded with

this timeout value. The hCccTimer is only decremented when

commands are outstanding on selected ports. The HBA will

signal a CCC interrupt when hCccTimer has decremented to

‘0’. The hCccTimer is reset to the timeout value on the

assertion of each CCC interrupt. A timeout value of ‘0’ is

reserved.

Command Completion Coalescing Ports - RW – 32 bits [Mem_reg: ABAR + 18h]

Field Name Bits Default Description

Ports (PRT) 31:0 00000000h This register is bit significant. Each bit corresponds to a

particular port, where bit 0 corresponds to port 0. If a bit is

set to ‘1’, the corresponding port is part of the command

completion coalescing feature. If a bit is cleared to ‘0’, the

port is not part of the command completion coalescing

feature. Bits set to ‘1’ in this register must also have the

corresponding bit set to ‘1’ in the Ports Implemented register.

An updated value for this field shall take effect within one

timer increment (1 millisecond).